# MAKING DISTRIBUTED COMPUTATION SECURE BY CONSTRUCTION

#### A Dissertation

Presented to the Faculty of the Graduate School of Cornell University

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

by

Lantian Zheng

January 2007

© 2007 Lantian Zheng

ALL RIGHTS RESERVED

#### MAKING DISTRIBUTED COMPUTATION SECURE BY CONSTRUCTION

Lantian Zheng, Ph.D.

#### Cornell University 2007

This thesis introduces new techniques to build distributed applications that are secure by construction, satisfying strong, end-to-end policies for confidentiality, integrity and availability. The new techniques are designed to solve the problem of how to specify, analyze and enforce end-to-end availability policies in distributed settings, without jeopardizing the enforcement of confidentiality and integrity policies. This thesis also presents a correctness proof for these techniques.

# **BIOGRAPHICAL SKETCH**

Lantian Zheng is a graduate student at the Computer Science Department of Cornell University. Lantian received his B.S. degree from Peking University and his M.S. degree from Cornell University.

To my parents

#### **ACKNOWLEDGEMENTS**

I have many people to thank for helping me complete this thesis. First and foremost is my advisor, Andrew Myers. I have learned a great deal from Andrew over the years. Without his guidance this thesis could not have been written.

I also owe a large debt to the other members of my thesis committee: Fred Schneider and Levent Orman. They provided invaluable advice in a timely fashion. I particularly want to thank Fred for his insightful feedback on drafts of this work.

I wish to express warm thanks to Steve Zdancewic, Nate Nystrom and Stephen Chong, who were my collaborators on the Jif/split project. Many of the ideas in this thesis were born out of the project.

Thanks go to Michael Clarkson for his feedback on early drafts of this thesis. Over the years, I have benefited from technical discussions with Andrei Sabelfeld, Lorenzo Alvisi, Heiko Mantel, Greg Morrisett, Wei Wei, Yong Yao, Jed Liu, Michael George, Krishnaprasad Vikram and Xin Qi. I would also like to thank Lidong Zhou for introducing me to the idea of quorum system.

I wish to thank my parents for all of their support during my never-ending education.

And thanks to Yuan for providing much-needed distractions.

# TABLE OF CONTENTS

| 1 | Intr                                                                | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.1                                                                 | Security by construction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |                                                                     | 1.1.1 Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                                     | 1.1.2 Secure program partitioning and replication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   |                                                                     | 1.1.3 What is new                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 1.2                                                                 | Enforcing availability policies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 1.3                                                                 | Proving correctness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 1.4                                                                 | Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 1.5                                                                 | Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 1.0                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2 | Uni                                                                 | versal decentralized label model 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 2.1                                                                 | Security properties, labels and policies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 2.2                                                                 | Dependency analysis and noninterference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 2.3                                                                 | Universal decentralized label model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |                                                                     | 2.3.1 Owned labels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                                                     | 2.3.2 Decentralized labels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                     | 2.3.3 Comparing labels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |                                                                     | 2.3.4 Information security labels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 2.4                                                                 | Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 2.5                                                                 | Related work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 2.5                                                                 | Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3 | The                                                                 | Aimp language 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3 | <b>The</b> 3.1                                                      | 1 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3 |                                                                     | 1 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3 | 3.1                                                                 | Syntax                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3 | 3.1<br>3.2                                                          | Syntax30Operational semantics31Examples33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3 | 3.1<br>3.2<br>3.3                                                   | Syntax30Operational semantics31Examples32Type system34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3 | 3.1<br>3.2<br>3.3<br>3.4                                            | Syntax30Operational semantics31Examples32Type system34Security by type checking39                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3 | 3.1<br>3.2<br>3.3<br>3.4                                            | Syntax30Operational semantics31Examples32Type system32Security by type checking323.5.1 Noninterference properties32                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3 | 3.1<br>3.2<br>3.3<br>3.4                                            | Syntax       30         Operational semantics       3         Examples       3         Type system       3         Security by type checking       3         3.5.1 Noninterference properties       3         3.5.2 The Aimp* language       4                                                                                                                                                                                                                                                                                                                |

| 3 | 3.1<br>3.2<br>3.3<br>3.4                                            | Syntax       30         Operational semantics       31         Examples       32         Type system       32         Security by type checking       32         3.5.1 Noninterference properties       32         3.5.2 The Aimp* language       42         3.5.3 Noninterference proof       57                                                                                                                                                                                                                                                             |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                     | Syntax       30         Operational semantics       31         Examples       32         Type system       32         Security by type checking       32         3.5.1 Noninterference properties       32         3.5.2 The Aimp* language       42         3.5.3 Noninterference proof       57                                                                                                                                                                                                                                                             |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                     | Syntax       30         Operational semantics       31         Examples       32         Type system       32         Security by type checking       32         3.5.1 Noninterference properties       32         3.5.2 The Aimp* language       44         3.5.3 Noninterference proof       57         Related work       59         are distributed computation       62                                                                                                                                                                                  |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                     | Syntax       30         Operational semantics       31         Examples       32         Type system       34         Security by type checking       39         3.5.1 Noninterference properties       39         3.5.2 The Aimp* language       44         3.5.3 Noninterference proof       57         Related work       59                                                                                                                                                                                                                               |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                     | Syntax       30         Operational semantics       31         Examples       32         Type system       32         Security by type checking       32         3.5.1 Noninterference properties       32         3.5.2 The Aimp* language       44         3.5.3 Noninterference proof       57         Related work       59         are distributed computation       62                                                                                                                                                                                  |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                     | Syntax       30         Operational semantics       31         Examples       32         Type system       34         Security by type checking       35         3.5.1 Noninterference properties       35         3.5.2 The Aimp* language       44         3.5.3 Noninterference proof       57         Related work       55         are distributed computation       62         System model       62         Reactors       64                                                                                                                          |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                     | Syntax       30         Operational semantics       31         Examples       32         Type system       32         Security by type checking       32         3.5.1 Noninterference properties       32         3.5.2 The Aimp* language       42         3.5.3 Noninterference proof       57         Related work       59         Ire distributed computation       62         System model       62         Reactors       64                                                                                                                          |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>Secu<br>4.1<br>4.2        | Syntax       30         Operational semantics       3         Examples       3         Type system       34         Security by type checking       35         3.5.1 Noninterference properties       39         3.5.2 The Aimp* language       44         3.5.3 Noninterference proof       57         Related work       59         Ire distributed computation       62         System model       62         Reactors       64         4.2.1 Example       67         Dynamic label checking       68                                                     |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>Secu<br>4.1<br>4.2<br>4.3 | Syntax       30         Operational semantics       3         Examples       3         Type system       32         Security by type checking       39         3.5.1 Noninterference properties       39         3.5.2 The Aimp* language       4         3.5.3 Noninterference proof       50         Related work       50         Irre distributed computation       60         System model       60         Reactors       60         4.2.1 Example       60         Dynamic label checking       60         Replication and message synthesis       72  |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>Secu<br>4.1<br>4.2<br>4.3 | Syntax       30         Operational semantics       3         Examples       3         Type system       32         Security by type checking       39         3.5.1 Noninterference properties       39         3.5.2 The Aimp* language       4         3.5.3 Noninterference proof       50         Related work       50         Inter distributed computation       60         System model       60         Reactors       60         4.2.1 Example       60         Dynamic label checking       60         Replication and message synthesis       70 |

|                 |      | 4.5.1 Tracking timestamps         | 79  |  |

|-----------------|------|-----------------------------------|-----|--|

|                 |      | 4.5.2 Quorum read                 | 80  |  |

|                 |      | 4.5.3 Quorum write                | 81  |  |

|                 | 4.6  | Multi-level timestamps            | 82  |  |

|                 | 4.7  | Example                           | 83  |  |

|                 | 4.8  | Related work                      | 85  |  |

| 5               | The  | DSR language                      | 88  |  |

|                 | 5.1  | Syntax                            | 88  |  |

|                 | 5.2  | Operational semantics             | 90  |  |

|                 | 5.3  | Type system                       | 96  |  |

|                 |      | 5.3.1 Subtyping                   | 97  |  |

|                 |      | 5.3.2 Typing                      | 98  |  |

|                 |      | 5.3.3 Subject reduction           | 101 |  |

|                 |      | 5.3.4 Preventing races            | 105 |  |

|                 | 5.4  | Noninterference                   | 107 |  |

|                 |      | 5.4.1 ζ-Consistency               | 109 |  |

|                 |      | 5.4.2 The DSR* language           | 113 |  |

|                 |      | 5.4.3 Noninterference proof       | 124 |  |

|                 | 5.5  | Related work                      | 129 |  |

| 6               | Secu | rity by construction              | 130 |  |

|                 | 6.1  | Splitter                          | 130 |  |

|                 |      | 6.1.1 Statement labels            | 131 |  |

|                 |      | 6.1.2 Secure distribution schemes | 133 |  |

|                 | 6.2  | Aimp/DSR translator               | 135 |  |

|                 |      | 6.2.1 Remote memory accesses      | 135 |  |

|                 |      | 6.2.2 Translation rules           | 136 |  |

|                 | 6.3  | Example                           | 142 |  |

|                 | 6.4  | Typing preservation               | 144 |  |

|                 | 6.5  | Semantics preservation            | 147 |  |

|                 | 6.6  | Related work                      | 160 |  |

| 7               | Cone | clusions                          | 162 |  |

| Bibliography 16 |      |                                   |     |  |

# LIST OF FIGURES

| 1.1 | Distributed implementations of the bidding application          |

|-----|-----------------------------------------------------------------|

| 1.2 | Bidding program                                                 |

| 1.3 | Security by construction                                        |

| 1.4 | Trustworthiness by construction                                 |

| 3.1 | Operational semantics for Aimp                                  |

| 3.2 | Examples                                                        |

| 3.3 | Bidding example                                                 |

| 3.4 | Typing rules for Aimp                                           |

| 3.5 | The operational semantics of Aimp*                              |

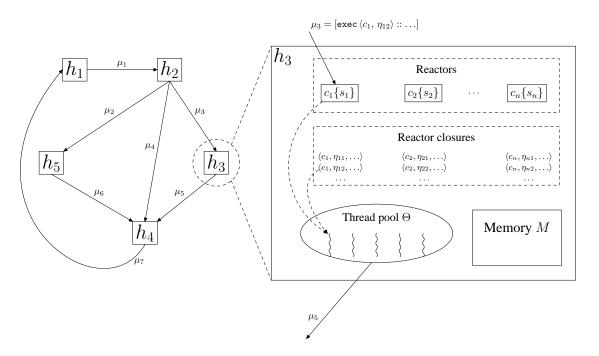

| 4.1 | System model                                                    |

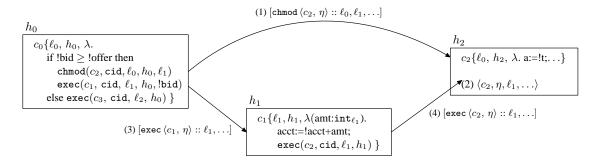

| 4.2 | A distributed program                                           |

| 4.3 | Linear entry creation                                           |

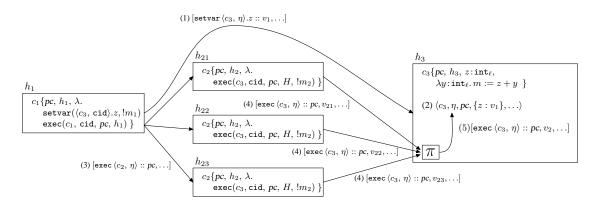

| 4.4 | Replication example                                             |

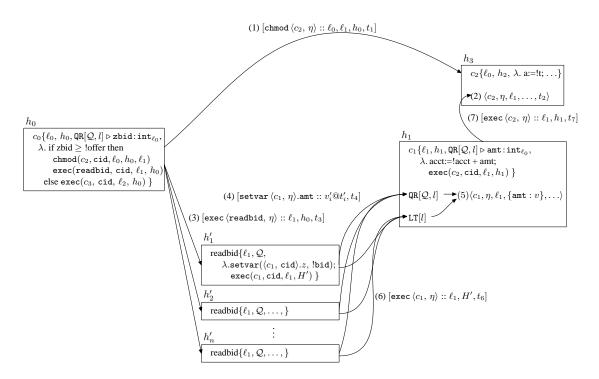

| 4.5 | Quorum replication and timestamps                               |

| 5.1 | Syntax of the DSR language                                      |

| 5.2 | Operational semantics of DSR with respect to $\Gamma$ and $P$ 9 |

| 5.3 | Subtyping rules                                                 |

| 5.4 | Typing rules of DSR                                             |

| 5.5 | $\zeta$ -Equivalence relation                                   |

| 5.6 | The operational semantics of DSR*                               |

| 5.7 | Typing rules of DSR*                                            |

| 6.1 | Rules for inferring statement labels                            |

| 6.2 | Aimp/DSR Translation rules                                      |

| 6.3 | The target DSR code of the bidding example                      |

# Chapter 1

# Introduction

Distributed computing systems are ubiquitous, yet it is currently difficult to make strong statements about the security provided by a distributed system as a whole, especially if some of the participants in a distributed computation do not trust other participants or the computing software and hardware they provide. Distributed systems serving mutually distrusting principals include clinical and financial information systems, business-to-business transactions, and joint military information systems.

This thesis proposes a unified approach (within a common framework of program analysis and transformation) to building distributed programs that enforce *end-to-end* confidentiality, integrity and availability policies, in a system with untrusted hosts.

Informally, an end-to-end confidentiality policy of data d specifies who can learn about d; an end-to-end integrity policy of d specifies who can affect d; an end-to-end availability policy of d specifies who can make d unavailable (d is available if the issuer of an authorized access request to d will eventually get the value of d). These policies regulate the behaviors of the whole system and can be viewed as an application of the end-to-end principle [74] to specifying security policies.

End-to-end confidentiality and integrity policies are also known as information flow policies, since they impose restrictions on how information is propagated throughout the system. Dynamic information flow control mechanisms, including mandatory access control (MAC) [9, 19], use run-time checks to ensure that information does not flow to a place protected by a weaker confidentiality policy or a stronger integrity policy. Although widely used in practice, those dynamic mechanisms suffer from high run-time overheads and covert exception channels associated with run-time security checks. Further, these dynamic mechanisms abort the programs that fail a run-time check, making it difficult to enforce availability policies. Denning [18] showed how to use static pro-

gram analysis to ensure that programs do not violate its information flow policies, and this approach has been instantiated in a number of languages in which the type system implements a similar static analysis (e.g., [88, 34, 102, 70, 7, 73]). Although static information flow control does not have the shortcomings of those dynamic mechanisms, it remains a challenge to develop a *sound* static analysis for distributed programs running in a system with untrusted hosts.

End-to-end availability policies specify availability requirements in terms of which principal can make the concerned data unavailable. The expressiveness of availability policies thus depends on the expressiveness of principals, which can represent not only users but also hardware, attacks or defense mechanisms, as shown in the following examples:

- power: the main power supply of a system, whose failure may bring down the entire system.

- hostset(n): a host set containing n hosts. This principal can be used to specify

the minimum number (n in this case) of host failures needed to bring down a

system. This is a common way of specifying availability requirements [75].

- puzzle: the puzzle generated by a puzzle-based defense mechanism [41] for DoS attacks. This principal can be used to specify the availability requirement that the system tolerates DoS attacks from attackers who cannot feasibly solve the puzzle.

Intuitively, end-to-end availability policies prevent attackers from making data unavailable. However, these policies do not ensure data to be available eventually. For example, a system may contain an infinite loop (such as an event handler), and any output to be produced after the loop will not be available, even if there are no attacks. A theoretical implication is that enforcing such availability policies does not require solving the halting problem [38].

## 1.1 Security by construction

Following the idea of static information flow control, a straightforward approach to building a secure distributed program is to develop a static program analysis that can determine whether a distributed program enforces its security policies. However, this *analytic approach* is not appealing for distributed systems composed of hosts that are heterogeneously trusted by different principals. In such a system, the distribution of data and computation depends on the *trust configuration*, that is, the trust relationship between principals and hosts. For example, Alice's confidential data can only be distributed to hosts that are trusted by Alice to protect data confidentiality. Such security concerns may be orthogonal to application logic, increasing the burden of software development. In addition, with this approach, programmers have to figure out how to adapt a program to changing trust configurations, and thus the burden of software maintenance is also increased.

This thesis pursues a *constructive approach*, which allows programmers to write high-level source program as if the program would be run on a single trusted host, and uses a compiler to translate the source program into a secure distributed program with respect to a given trust configuration. Programmers can thus focus on the application logic. Moreover, if the trust configuration changes, a mere recompilation of the source code with respect to the new configuration will generate a new secure distributed program.

# **1.1.1 Example**

The advantages of the constructive approach can be illustrated by a simple example. Suppose Alice tries to bid for something from Bob, and Bob has three items that satisfy Alice's requirement and offers a price for each item. The offers are stored in an ordered

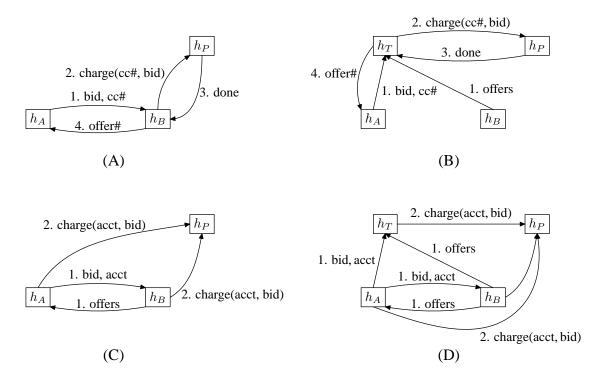

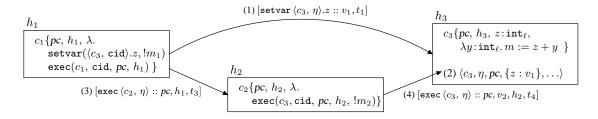

Figure 1.1: Distributed implementations of the bidding application

list, and Alice is forced to accept the first offer in the list that is lower than or equal to her bid. During the transaction, Alice and Bob should not be able to update the bid or the offers, and they should not be able to abort the transaction alone.

#### Using the analytic approach

Figure 1.1 shows several distributed implementations of the application. For simplicity, only network messages are shown, which are labeled with sequence numbers indicating their order of occurrence. The computations done at each local host are described below:

(A) Host  $h_A$  (a host fully controlled and trusted by Alice) sends Alice's credit card number and bid to host  $h_B$  (a host fully controlled and trusted by Bob). Then  $h_B$  compares the bid with Bob's offers and sends a payment request to host  $h_P$ , which handles charging Alice's credit card account. Once  $h_B$  gets a response from  $h_P$ , it sends the offer number to  $h_A$ . This implementation corresponds to the common

scenario in which Alice places the bid on a web site managed by Bob.

There are several security problems with this implementation. First, Alice may not trust  $h_B$  to keep her credit card number confidential. Second, Bob has the full control of  $h_B$ , and is able to change the bid and the offers, or simply abort the transaction.

- (B) Suppose host  $h_T$  is trusted by both Alice and Bob. Then  $h_A$  and  $h_B$  can send all the data to  $h_T$ , which compares Alice's bid with Bob's offers and sends the payment request to  $h_P$ . This implementation relies on the existence of a host fully trusted by all the participating principals.

- (C) Suppose the system is composed of only  $h_A$ ,  $h_B$  and  $h_P$ . There are still ways to improve security over implementation (A). First, Alice's credit card number is simply a reference to Alice's payment account, and it is possible to use a public identifier acct as the account reference, such as the email address in the Pay-Pal service. Second, the data (including the bid and the offers) and computation can be replicated on  $h_A$  and  $h_B$ , which both send the payment request to  $h_P$ . If the requests from  $h_A$  and  $h_B$  are not the same,  $h_P$  can detect that some host is compromised and abort the transaction. Therefore, Alice or Bob cannot modify the bid and the offers without being detected. The main problem with this implementation is that either  $h_A$  and  $h_B$  can send a fabricated request and cause the transaction to be aborted.

- (D) Suppose Alice and Bob do not fully trust  $h_T$ . Instead, they trust that at most one host among  $h_A$ ,  $h_B$  and  $h_T$  might fail. Then Alice and Bob would be satisfied with the security assurance of this implementation, in which the data and computation is also replicated on  $h_A$ ,  $h_B$  and  $h_T$ , and host  $h_P$  accepts the payment request if the request comes from both  $h_A$  and  $h_B$  or from  $h_T$ .

```

1 t := 0; a := -1;

2 while (t < 3) do

3    if (bid >= offer[t]) then acct := acct - bid; a := t; break;

4    else t := t + 1;

5 result := a;

```

Figure 1.2: Bidding program

As Figure 1.1 shows, determining how to securely distribute and replicate data and computation may be subtle and error-prone. Further, if the corresponding trust configuration changes, a distributed program may need to undergo significant modification to adapt to the new configuration. For example, in (B), if  $h_T$  is detected to be compromised, and there are no other hosts trusted by both Alice and Bob, then the program needs to be redesigned.

#### Using the constructive approach

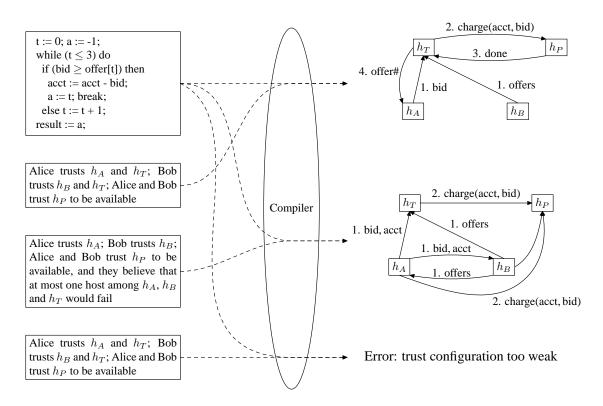

Although the implementations in Figure 1.1 are different, they all try to perform the same computation, which can be described by the sequential program shown in Figure 1.2. Using the constructive approach, this simple program is all that needs to be written by programmers.

As Figure 1.3 shows, given the source program and a trust configuration, a compiler generates a secure distributed program or report an error when there are not enough trusted hosts in the system. With this approach, programmers can focus on application logic, since the trust configuration of the system is transparent to them. Further, only recompilation is needed to cope with changing trust configurations.

# 1.1.2 Secure program partitioning and replication

Earlier work on the Jif/split system [104, 105] explored the constructive approach, using end-to-end confidentiality and integrity policies to guide automatic partitioning and

Figure 1.3: Security by construction

replication of code and data onto a distributed system.

In the Jif/split system, source programs are written in Jif [62, 65], which extends Java with type-based static information flow control. The Jif/split compiler translates a source program into a distributed Java program that enforces the information flow policies specified as type annotations in the source.

#### 1.1.3 What is new

The Jif/split system demonstrates the feasibility of the constructive approach to building secure distributed programs. However, the Jif/split system does not support end-to-end availability policies, and there is no correctness proof for the translation algorithm of the Jif/split compiler, partially because of the complexity of the Jif language.

In comparison to the work on the Jif/split system, this thesis makes two major contri-

butions. First, this thesis proposes a way of analyzing and enforcing availability policies, based on the idea of static information flow control. Second, this thesis formalizes the core part of the Jif/split translation, extends it with support for availability, and proves the correctness of the translation.

## 1.2 Enforcing availability policies

Although availability is often considered one of the three key aspects of information security (along with confidentiality and integrity), availability assurance has been largely divorced from other security concerns. This thesis starts to bridge the gap by providing a unified way of specifying, analyzing and enforcing end-to-end confidentiality, integrity and availability policies.

End-to-end confidentiality and integrity policies can be enforced by ensuring that the system obey noninterference [31]. In general, an end-to-end availability policy on some data d specifies that principals  $p_1, \ldots, p_n$  can make d unavailable, and such a policy can also be enforced by a form of noninterference: principals other than  $p_1, \ldots, p_n$  do not interfere with the availability of d. This suggests that the idea of static information flow control can be applied to availability too. This thesis introduces a sequential language Aimp with a security type system that ensures a well-typed program satisfies the noninterference properties that enforce the end-to-end policies (including availability policies) specified as type annotations.

An interesting challenge in designing the Aimp type system is to analyze the dependencies between integrity and availability. Consider the code in Figure 1.2. Attackers can make the output result unavailable by compromising the integrity of t (making t always less than 3). Intuitively, the integrity policy of t needs to be as strong as the availability policy of result. To enable comparing an integrity policy with an availability policy, this thesis proposes a universal label model, in which confidentiality, integrity

and availability labels have the same form and the same interpretation.

To enforce availability policies in a distributed setting, this thesis presents the DSR (Distributed Secure Reactors) language for describing distributed, concurrent computation on replicated hosts. The DSR language makes the following specific contributions related to enforcing availability policies:

- The DSR language supports quorum replication [30, 35], which is extended to be guided by explicit security policies. Voting replicas can enforce both integrity and availability policies.

- A novel timestamp scheme is used to coordinate concurrent computations running on different replicas, without introducing covert channels.

Applying the constructive approach, this thesis presents a translation from Aimp to DSR, which generates a secure distributed DSR program from an Aimp program and a trust configuration. The translation automatically figures out how to replicate data and code in quorum systems to enforce integrity and availability policies.

# 1.3 Proving correctness

In Aimp and DSR, security policies are explicitly defined using *labels* that annotate data items, computations, hosts and principals with security levels. In a system with mutually distrusted principals, attackers are treated as principals that have the power to affect certain behaviors of the system. The power of attackers is represented by a label  $l_A$ . A label is *low-security* if it is lower than or equal to  $l_A$ , and *high-security* otherwise. Intuitively, the policies specified by labels require that attackers cannot learn information about data with high-confidentiality labels, affect data with high-integrity labels, or make data with high-availability labels unavailable. Thus, a system is secure if the following three noninterference [31] properties are satisfied:

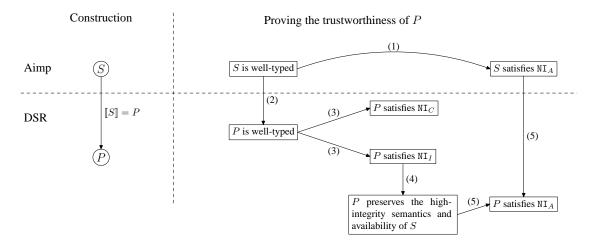

Figure 1.4: Trustworthiness by construction

- Confidentiality noninterference (NI<sub>C</sub>): attackers cannot infer high-confidentiality

data, or high-confidentiality inputs cannot interfere with low-confidentiality outputs that are observable to attackers.

- Integrity noninterference (NI<sub>I</sub>): attackers cannot affect high-integrity data.

- Availability noninterference (NI<sub>A</sub>): attackers cannot affect the availability of data with high-availability labels.

With these concepts, our goal is to prove that the Aimp-DSR translation generates distributed programs that satisfy  $NI_C$ ,  $NI_I$ , and  $NI_A$ .

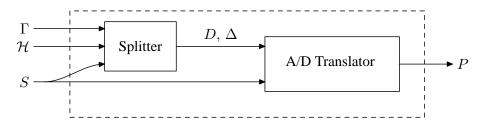

Figure 1.4 shows the proof strategy. A well-typed program S in Aimp is translated into a DSR program P, and the translation is denoted by  $[\![S]\!] = P$ . The proof that P satisfies the noninterference properties is done in the following steps.

- (1) We show that the type system of Aimp ensures that a well-typed program satisfies the noninterference properties. Since S is well-typed, S satisfies  $NI_A$ .

- (2) We show that the translation preserves sound typing. Thus, P is well-typed because S is well-typed.

- (3) We show that the type system of DSR enforces the confidentiality and integrity

noninterference properties. Therefore, P satisfies  $NI_C$  and  $NI_I$ , because P is well-typed.

- (4) We show that P always produces the same high-integrity outputs as S despite attacks from low-integrity hosts, and P can achieve the same level of availability as S. In other words, if S produces a high-availability output, then P also produces that output, although the output may be different if it is low-integrity. The proof relies on the fact that P satisfies  $NI_I$ , which means attackers cannot affect the high-integrity outputs even if they can compromise some low-integrity hosts and launch attacks from them.

- (5) We show that P satisfies  $NI_A$ , based on that P can achieve the same availability as S, and S satisfies  $NI_A$ .

#### 1.4 Limitations

The Aimp/DSR instantiation of the constructive approach to building secure distributed programs has a few limitations. First, source language Aimp is a sequential language and cannot be used to express concurrent computation. However, many useful applications, including the bidding example in Figure 1.2, are sequential.

Second, the DSR type system does not deal with timing channels. Since Aimp is sequential, a target DSR program generated from an Aimp program does not cause race conditions and internal timing channels [103]. Attackers may still be able to infer confidential information by timing the network messages they can observe. However, this kind of timing channels is more noisy than internal timing channels, and it is largely an orthogonal issue, partially addressed by ongoing work [3, 72].

Third, in a distributed system, attackers can cause certain execution paths to diverge (going into an infinite loop or getting stuck) by compromising some hosts, and create termination channels. This issue is also not addressed in this thesis, partly because termination channels generally have low bandwidth.

Finally, in this thesis, the formal notion of availability glosses over another aspect of availability: timeliness. How soon does an output have to occur in order to be considered to be available? For real-time services, there may be hard time bounds beyond which a late output is useless. Reasoning about how long it takes to generate an output adds considerable complexity, and this is left for future work.

#### 1.5 Outline

The remainder of this thesis is organized as follows. Chapter 2 describes the universal label model for specifying end-to-end security policies. Chapter 3 describes source language Aimp. Chapter 4 describes the features and mechanisms in DSR, which support performing secure distributed computation. Chapter 5 presents the formal semantics of DSR and proves the type system of DSR enforces confidentiality and integrity noninterference properties. Chapter 6 presents a translation from Aimp to DSR, and prove that the translation generates secure distributed programs. Chapter 7 concludes.

# Chapter 2

# Universal decentralized label model

A label model describes how to specify and analyze *security labels*, which are associated with data to describe the security levels of data and help characterize the restrictions on data generation and uses. Formally, a label model is a set of labels  $\mathcal{L}$  with a partial order relation  $\leq$ . For example, {public, secret} with  $\leq$  being {(public, public), (public, secret), (secret, secret)} forms a simple confidentiality label model, in which secret represents a higher confidentiality level than public.

The *decentralized label model* (DLM) [64] allows different users to specify their own information flow policies in a security label. The DLM is suitable for a system with mutual distrust, in which different users might have different security requirements.

This chapter introduces a universal DLM, which extends the DLM with support for specifying and analyzing availability labels. The universal DLM is composed of a set of *decentralized labels*, each of which can be used as a confidentiality, integrity or availability label. This is possible due to a uniform semantics for decentralized labels, which interprets a label as a security assumption. Besides simplicity, the major benefit of the universal DLM is to support analyzing interactions between integrity and availability.

# 2.1 Security properties, labels and policies

This thesis focuses on the three core security properties on information: confidentiality, integrity and availability. In the security literature, the three properties (especially integrity and availability) have many different meanings [69, 12]. In this thesis, a security property  $\rho$ , which may represent the confidentiality, integrity or availability of data d, is written and interpreted as follows:

• confidentiality(d), meaning that attackers cannot learn about data d,

- integrity(d), meaning that attackers cannot affect the value of d, or

- availability(d), meaning that attackers cannot make d unavailable.

A security property is often treated as a predicate on the set of all traces of a system. For example, Zakinthinos and Lee [100] define a security (confidentiality) property as a predicate that a system satisfies if and only if for any trace  $\tau$  of the system, the set of traces that attackers cannot distinguish from  $\tau$  satisfy another specific predicate. In particular, their work shows that a noninterference property can be defined as such a predicate. The security properties considered in this thesis are also closely related to the notion of noninterference. Intuitively, a system enforces *confidentiality*(d) if and only if the value of d does not interfere with any data observable to attackers; a system enforces *integrity*(d) and *availability*(d) if and only if attackers cannot interfere with the value and availability of d, respectively. Therefore, a security property  $\rho$  can also be viewed as a predicate on the set of all traces of a system.

#### **Security assumptions as labels**

It is infeasible to enforce a security property if attackers have unconstrained power, and security rests on assumptions that constrain the power of attackers. For example, security commonly depends on a trusted computing base (TCB), which is assumed immune to attacks. Furthermore, security assumptions help define the restrictions on the use of data. For example, consider enforcing *confidentiality*(d) under the assumption that user root is trusted, which says that root is not controlled by attackers. According to the assumption, root may be allowed to learn about d, but not other principals. Defining the restrictions on the use of data is also the purpose of security labels. Thus, it is natural to specify security assumptions as labels. Formally, if a label l is associated with property  $\rho$ , then the semantics of l, written as [l], describes the security assumptions for enforcing  $\rho$ .

#### **Security policies**

A label l specified on property  $\rho$  defines a *security policy*  $\langle \rho : l \rangle$ , which is enforced by a system  $\mathcal{S}$  if and only if  $\mathcal{S}$  satisfies  $\rho$  under the assumption  $[\![l]\!]$ , or more formally,  $[\![l]\!] \Rightarrow \rho(\mathcal{S})$ , where  $\rho(\mathcal{S})$  denotes that  $\mathcal{S}$  satisfies  $\rho$ , and  $\Rightarrow$  means "implies". For example,  $\langle confidentiality(d) : l \rangle$  is a confidentiality policy on d, and it is enforced if attackers cannot learn about d under the assumption  $[\![l]\!]$ . Enforcing the policy  $\langle \rho : l \rangle$  is also called "enforcing l on  $\rho$ ", or simply "enforcing l" if there is no ambiguity about  $\rho$ . For brevity, in a logical proposition, we write  $\rho$  for  $\rho(\mathcal{S})$  if it is clear which system is under consideration. For example,  $[\![l]\!] \Rightarrow \rho(\mathcal{S})$  can be written as  $[\![l]\!] \Rightarrow \rho$  if there is no ambiguity about  $\mathcal{S}$ .

In this thesis, a system is considered *secure* if it does not violate any policy of the form  $\langle \rho : l \rangle$  specified on its data.

## 2.2 Dependency analysis and noninterference

A computing system processes inputs and produces outputs, creating dependencies between security properties of those inputs and outputs. Such dependencies capture the system vulnerabilities that can be exploited by attackers to compromise security properties. For example, consider a system running the following pseudo-code:

```

while (i > 0) skip;

o := i;

```

This program assigns the input i to the output o if the value of i is not positive. Otherwise, the program diverges and the output is unavailable. Thus, the availability of o depends on the integrity of i. An attacker can try to exploit this dependency: making o unavailable by affecting the value of i to make it positive.

In a system S, property  $\rho$  depends on  $\rho_1 \vee \ldots \vee \rho_n$ , written  $\rho_1 \vee \ldots \vee \rho_n \rightsquigarrow \rho$ , if the proposition  $\neg(\rho_1(S) \vee \ldots \vee \rho_n(S)) \Rightarrow \neg \rho(S)$  holds, that is, if all properties  $\rho_1$  through  $\rho_n$  are *not* satisfied in S, then  $\rho$  is *not* satisfied in S. In general, the dependencies caused by a system can be identified by statically analyzing the code of a system. For example, by analyzing the code of the above system, we know that the value of o is computed using the value of o, and the availability of o is affected by the value of o. Therefore, the system causes the following dependencies:

$$confidentiality(o) \leadsto confidentiality(i)$$

$integrity(i) \leadsto integrity(o)$

$availability(i) \leadsto availability(o)$

$integrity(i) \leadsto availability(o)$

We assume that an attacker can interact with a system only by affecting the inputs and observing the outputs. The interactions between attackers and inputs/outputs of a system always mean that some security properties are compromised: if attackers can observe an output, then the confidentiality of the output is compromised; if attackers can affect the value of an input, then the integrity of the input is compromised; and if attackers can affect the availability of an input, then the availability of the input is compromised.

In addition, we assume that a policy is enforced in a system if the enforcement of the policy is affected not by the system, but by the external environment. In particular, a system cannot affect how its inputs are generated and how its outputs are used, and thus the integrity and availability policies on inputs, and the confidentiality policies on outputs are assumed to be enforced. This is called the *safe environment* assumption. Based on this assumption, we have the following theorem, which gives a sufficient condition for ensuring that a system is secure.

**Theorem 2.2.1 (Dependency).** Let  $l_{\rho}$  be the label specified on property  $\rho$ . A system is

secure if it satisfies the following condition:

$$\forall \rho, \rho_1, \dots, \rho_n \colon (\rho_1 \vee \dots \vee \rho_n \leadsto \rho) \Rightarrow (\llbracket l_\rho \rrbracket) \Rightarrow \llbracket l_{\rho_1} \rrbracket \vee \dots \vee \llbracket l_{\rho_n} \rrbracket) \tag{DP}$$

*Proof.* Suppose, by way of contradiction, that the system is not secure and violates a policy  $\langle \rho : l_{\rho} \rangle$ . Then  $[\![l_{\rho}]\!] \Rightarrow \rho$  does not hold, which implies  $[\![l_{\rho}]\!] \wedge \neg \rho$ . Since  $[\![l_{\rho}]\!]$  holds, by the safe environment assumption, attackers cannot compromise  $\rho$  directly without exploiting the system. Therefore,  $\rho$  is compromised because of some interactions between attackers and the system. As discussed above, those interactions mean that a set of properties  $\rho_1, \ldots, \rho_n$  are compromised directly, and for all i in  $\{1, \ldots, n\}$ , the enforcement of policy  $\langle \rho_i : l_{\rho_i} \rangle$  is not affected by the system. By the safe environment assumption,  $\langle \rho_i : l_{\rho_i} \rangle$  is enforced, and  $[\![l_{\rho_i}]\!]$  does not hold for all  $i \in \{1, \ldots, n\}$ . Since  $\rho$  is compromised due to those interactions, we have  $\neg \rho_1 \wedge \ldots \wedge \neg \rho_1 \Rightarrow \neg \rho$ , that is,  $\rho_1 \vee \ldots \vee \rho_n \rightsquigarrow \rho$ . By DP, we have  $[\![l_{\rho}]\!] \Rightarrow [\![l_{\rho_1}]\!] \vee \ldots \vee [\![l_{\rho_n}]\!]$ , which contradicts the fact that  $[\![l_{\rho}]\!]$  holds, and  $[\![l_{\rho_i}]\!]$  does not hold for  $i \in \{1, \ldots, n\}$ .

By Theorem 2.2.1, a system is secure if it satisfies the following condition that is equivalent to DP:

$$\forall \rho_1, \dots, \rho_n, \rho. (\llbracket l_\rho) \rrbracket \not\Rightarrow \llbracket l_{\rho_1} \rrbracket \vee \dots \vee \llbracket l_{\rho_n} \rrbracket) \Rightarrow \rho_1 \vee \dots \vee \rho_n \not\rightsquigarrow \rho$$

(NI)

The condition NI says that  $\rho$  does not depend on  $\rho_1 \vee \ldots \vee \rho_n$ , unless their labels satisfy  $[\![l_\rho]\!] \Rightarrow \bigvee_{1 \leq i \leq n} [\![l_{\rho_i}]\!]$ . The notion of independence between properties is often formalized a noninterference [31] property. In practice, DP helps construct a program dependency analysis and identify the label constraints that need to be verified, while NI is often used as a semantic security condition in proving the correctness of an enforcement mechanism. For both conditions, we only need to reason about the label constraints of the form  $[\![l]\!] \Rightarrow [\![l_1]\!] \vee \ldots \vee [\![l_n]\!]$  and the dependencies between security properties. In particular, we do not need to directly reason whether  $[\![l]\!] \Rightarrow \rho$  holds.

#### 2.3 Universal decentralized label model

In the security model discussed in Section 2.1, a security label is interpreted as a security assumption, regardless of what kind of security property that the label is specified on. As a result, it is possible to construct a universal label model applicable to confidentiality, integrity and availability simultaneously. This is desirable because it allows us to compare labels specified on different kinds of properties. For example, we can compare an integrity label with an availability label, and reason about dependencies between integrity and availability.

This section extends the DLM to make it universally applicable to confidentiality, integrity and availability. And a uniform semantics for labels is presented.

#### 2.3.1 Owned labels

The DLM is designed to let users specify and manage their own confidentiality and integrity labels. Thus, it is necessary to be able to identify the owner of a label. To achieve this ability, the DLM is built on *owned labels*, in which label owners are specified explicitly. An owned label O has the form u:p, where user principal u is the owner of the label, and p is a principal, representing the system entities that u considers non-compromised (not falling under the control of attackers).

This section describes the syntax and semantics of owned labels. The formalization borrows some ideas from the access control calculus [1] designed by Abadi, Burrows, Lampson and Plotkin.

#### **Principals**

Formally, principals are specified using the following syntax:

Principals

$$u, p ::= a \mid * \mid p_1 \land p_2 \mid p_1 \lor p_2$$

The meta-variable a is an abstract name representing an atomic entity that may affect the behavior of a system. For example, a may be used to represent a user, a host, the power supply or other system components. Principal \* is a top principal who acts for every principal. In general, principal  $p_1$  acts for principal  $p_2$ , written as  $p_1 \succeq p_2$ , if  $p_1$  can act with the full authority of  $p_2$ , or in other words, any behavior by  $p_1$  can be viewed as a behavior by  $p_2$ . The  $\succeq$  relation is reflexive and transitive.

Another useful relation between principals is the *speaks-for* relation [1]:  $p_1$  speaks for  $p_2$  if any claim made by  $p_1$  can be viewed as a claim made by  $p_2$ . Intuitively, the acts-for relation is stronger than the speaks-for relation, since making a claim is just one kind of behaviors that a principal may perform.

It is possible to construct more complex principals using conjunction and disjunction operators [1]:  $\wedge$  and  $\vee$ . The composite principal  $p_1 \wedge p_2$  is the principal with exactly the authority of both  $p_1$  and  $p_2$ . Any behavior by both  $p_1$  and  $p_2$  is viewed as a behavior by  $p_1 \wedge p_2$ , and vice versa. It is clear that  $p_1 \wedge p_2$  is the least upper bound of  $p_1$  and  $p_2$  with respect to the  $\succeq$  ordering. More concretely,  $p_1 \wedge p_2$  acts for  $p_1$  and  $p_2$ ; and if principal  $p_2$  acts for  $p_1$  and  $p_2$ , then  $p_2$  also acts for  $p_1 \wedge p_2$ .

Another constructor  $\vee$  is used to construct a group (disjunction): any behavior by  $p_1$  or  $p_2$  is considered a behavior of  $p_1 \vee p_2$ , and vice versa. There are other meaningful principal constructors such as "a as R" (the principal a in role R) [1, 25], and  $\neg a$  (the *negative* principal of a), which represents the principal who has all the authorities that a does not have. The negative principal can be used to specify the *separation of duties* [14]. Suppose data d can be read only by principal a, and data d' only by  $\neg a$ . Then no principal other than the top principal can read both d and d'. This thesis only considers the conjunctive and disjunctive connectors because these two connectors are sufficient for specifying expressive end-to-end policies.

We assume that a principal is either compromised or non-compromised. A compro-

mised principal is controlled by attackers, while a non-compromised principal is not. More formally, let A be the principal representing all the attackers. Then a principal p is compromised if and only if  $A \succeq p$ .

#### **Semantics**

The owned label u:p explicitly expresses the assumption by u that p is non-compromised. As the label owner, user u is able to affect the implications of this label by making claims about the acts-for relations or whether other principals are non-compromised. For example, u may claim  $p' \succeq p$ . Then label u:p also implies that p' is non-compromised. In general, label u:p conveys an implicit assumption that u is honest, meaning that every claim made by u is true.

Note that a non-compromised principal is not necessarily honest. Furthermore, we do not assume that a compromised principal is dishonest because the assumption is not essential, albeit intuitive.

Formally, a security assumption can be expressed by a proposition  $\sigma$  with the following syntax:

$$\sigma ::= \operatorname{good} p \mid p \operatorname{says} \sigma \mid \operatorname{honest} p \mid p_1 \succeq p_2 \mid \sigma_1 \wedge \sigma_2 \mid \sigma_1 \vee \sigma_2$$

The interpretation is straightforward:  $good\ p$  means that p is non-compromised; p says  $\sigma$  means that p claims  $\sigma$ ; honest p means that p is honest  $(\forall \sigma.\ p\ says\ \sigma \Rightarrow \sigma)$ ;  $p_1 \succeq p_2$  means that  $p_1$  acts for  $p_2$ . The connectors  $\wedge$  and  $\vee$  are the standard propositional "and" and "or". With this language, the semantics of label u:p is as follows:

$$[\![u\!:\!p]\!] = \mathit{honest}\, u \wedge \mathit{good}\, p$$

By the meaning of  $p_1 \succeq p_2$ , it is clear that  $p_1 \succeq p_2$  implies  $good\ p_2 \Rightarrow good\ p_1$ ,  $p_1\ says\ \sigma \Rightarrow p_2\ says\ \sigma$ , and honest  $p_1 \Rightarrow honest\ p_2$ . By the definition of  $p_1 \land p_2$ , we

immediately have the following inference rules:

R1.

$$good p_1 \vee good p_2 \Leftrightarrow good (p_1 \wedge p_2)$$

R2.

$$p_1$$

says  $\sigma \wedge p_2$  says  $\sigma \Leftrightarrow p_1 \wedge p_2$  says  $\sigma$

Dually, we have the following rules with  $p_1 \lor p_2$ :

R3.

$$good p_1 \wedge good p_2 \Leftrightarrow good (p_1 \vee p_2)$$

R4.

$$p_1$$

says  $\sigma \lor p_2$  says  $\sigma \Leftrightarrow p_1 \lor p_2$  says  $\sigma$

By rule (R4), we can prove the following lemma:

**Lemma 2.3.1.** honest  $p_1 \lor p_2 \Leftrightarrow \text{honest } p_1 \land \text{honest } p_2$

Proof.

honest

$$p_1 \vee p_2$$

$$\Leftrightarrow \forall \sigma. \ p_1 \lor p_2 \ says \ \sigma \Rightarrow \sigma$$

$$\Leftrightarrow \forall \sigma. \ p_1 \ \text{says} \ \sigma \lor p_2 \ \text{says} \ \sigma \Rightarrow \sigma$$

$$\Leftrightarrow \forall \sigma. (p_1 \text{ says } \sigma \Rightarrow \sigma) \land (p_2 \text{ says } \sigma \Rightarrow \sigma)$$

$$\Leftrightarrow (\forall \sigma. \ p_1 \ \text{says} \ \sigma \Rightarrow \sigma) \land (\forall \sigma. \ p_2 \ \text{says} \ \sigma \Rightarrow \sigma)$$

$\Leftrightarrow$  honest  $p_1 \wedge$  honest  $p_2$

2.3.2 Decentralized labels

Owned labels allow different principals to specify and manage their security requirements. Multiple owned labels  $O_1, \ldots, O_n$  may be specified on the same security property  $\rho$ . A secure system needs to enforce all these labels  $O_1, \ldots, O_n$  on  $\rho$ , which amounts to ensuring  $\forall i \in \{1, \ldots, n\}$ .  $\llbracket O_i \rrbracket \Rightarrow \rho$ , or equivalently,  $(\bigvee_{1 \leq i \leq n} \llbracket O_i \rrbracket) \Rightarrow \rho$ .

Based on this observation, we can write  $O_1, \ldots, O_n$  together as a single label  $l = \{O_1, \ldots, O_n\}$  and let  $[\![l]\!] = \bigvee_{1 \leq i \leq n} [\![O_i]\!]$ . Then specifying and enforcing  $O_1, \ldots, O_n$  on  $\rho$  is equivalent to specifying and enforcing l on  $\rho$ . The label l is called a *decentralized*

*label* because it incorporates security requirements of different principals that generally do not fall under a centralized authority. Now the security requirements with regard to a security property can be described by a single label, even in a distributed system with mutual distrust. This greatly simplifies security analysis.

## 2.3.3 Comparing labels

A label  $l_2$  is as high as another label  $l_1$ , written as  $l_1 \leq l_2$ , if the enforcement of  $l_2$  on any property  $\rho$  implies the enforcement of  $l_1$  on  $\rho$ . Intuitively, if  $\rho$  is enforced under a weak assumption, then  $\rho$  is also enforced under a strong assumption. Therefore,  $l_1 \leq l_2$  if and only if  $[\![l_1]\!]$  is as strong as  $[\![l_2]\!]$ , or  $[\![l_1]\!] \Rightarrow [\![l_2]\!]$ . By the semantics of owned labels, the following rule for comparing owned labels immediately follows:

$$\frac{u_2 \succeq u_1 \quad p_2 \succeq p_1}{u_1 \colon p_1 \le u_2 \colon p_2}$$

Consider two decentralized labels  $l_1$  and  $l_2$ . Intuitively, if for any owned label O in  $l_1$ , there exists an owned label in  $l_2$  that is as high as O, then  $l_2$  is as high as  $l_1$ . Formally, it is easy to show that  $(\forall O \in l_1. \exists O' \in l_2. O \leq O')$  implies  $[\![l_1]\!] \Rightarrow [\![l_2]\!]$ . Thus, we have the following inference rule for comparing decentralized labels:

$$\frac{\forall O \in l_1. \ \exists O' \in l_2. \ O \le O'}{l_1 \le l_2}$$

The set of all the decentralized labels form a lattice with the following join ( $\Box$ ) and meet ( $\Box$ ) operations:

$$l_1 \sqcup l_2 = l_1 \cup l_2$$

$l_1 \sqcap l_2 = \{u_1 \lor u_2 : p_1 \lor p_2 \mid u_1 : p_1 \in l_1 \land u_2 : p_2 \in l_2\}$

The join and meet operations are well-defined because of the following theorem, which implies that  $l_1 \sqcup l_2$  is the least upper bound of  $l_1$  and  $l_2$  with respect to the  $\leq$  ordering, and  $l_1 \sqcap l_2$  is the greatest lower bound of  $l_1$  and  $l_2$ .

**Theorem 2.3.1.**

$$[\![l \sqcup l']\!] = [\![l]\!] \vee [\![l']\!]$$

and  $[\![l \sqcap l']\!] = [\![l]\!] \wedge [\![l']\!]$ .

*Proof.* Suppose  $l = \{O_1, ..., O_n\}$  and  $l' = \{O'_1, ..., O'_m\}$ , and  $O_i = u_i : p_i$  and  $O'_j = u'_j : p'_j$ . Then  $l \sqcup l' = \{O_1, ..., O_n, O'_1, ..., O'_m\}$ . Thus,

$$[\![l \sqcup l']\!] = (\bigvee_{1 \le i \le n} [\![O_i]\!]) \vee (\bigvee_{1 \le i \le m} [\![O_i']\!]) = [\![l]\!] \vee [\![l']\!].$$

For  $l \sqcap l'$ , we have the following deduction:

By the definition of the join operation,  $\bot = \emptyset$  is the bottom of the decentralized label lattice, since  $\forall l. \ \emptyset \sqcup l = l$ . Intuitively, the bottom label represents the strongest security assumption, and thus  $\llbracket \emptyset \rrbracket$  is the proposition false. The top element of the decentralized label lattice is  $\top = \{*:*\}$ , because for any owned label u:p, we have  $u:p \le *:*$ .

Having a lattice of labels supports static program analysis [18]. For example, consider an addition expression  $e_1 + e_2$ . Let  $A(e_1)$  and  $A(e_2)$  represent the availability labels of the results of  $e_1$  and  $e_2$ . By condition DP, we have  $A(e_1 + e_2) \leq A(e_1)$  and  $A(e_1 + e_2) \leq A(e_2)$ , since the result of  $e_1 + e_2$  is available if and only if the results of  $e_1$  and  $e_2$  are both available. Because the labels form a lattice,  $A(e_1 + e_2) = A(e_1) \sqcap A(e_2)$  is the least restrictive availability label we can assign to the result of  $e_1 + e_2$ . Similarly,  $I(e_1 + e_2) = I(e_1) \sqcap I(e_2)$  is the least restrictive integrity label for the result of  $e_1 + e_2$ ,

where  $I(e_1)$  and  $I(e_2)$  are respectively the integrity labels of  $e_1$  and  $e_2$ . Dually, if  $C(e_1)$  and  $C(e_2)$  are the confidentiality labels of  $e_1$  and  $e_2$ , then  $C(e_1) \leq C(e_1 + e_2)$  and  $C(e_2) \leq C(e_1 + e_2)$ . The least restrictive confidentiality label that can be assigned to the result of  $e_1 + e_2$  is  $C(e_1) \sqcup C(e_2)$ .

In addition, with a lattice label model, the DP and NI conditions can be written as:

$$\forall \rho, \rho_1, \dots, \rho_n. \ (\rho_1 \vee \dots \vee \rho_n \leadsto \rho) \Rightarrow (l_\rho \leq l_{\rho_1} \sqcup \dots \sqcup l_{\rho_n})$$

(DP)

$$\forall \rho, \rho_1, \dots, \rho_n. \ (l_\rho \not\leq l_{\rho_1} \sqcup \dots \sqcup l_{\rho_n}) \Rightarrow \rho_1 \vee \dots \vee \rho_n \not\rightsquigarrow \rho \tag{NI}$$

## 2.3.4 Information security labels

In general, a system will need to simultaneously enforce labels on confidentiality, integrity, and availability for the information it manipulates. These labels can be applied to information as a single security label, which have the following syntax:

Property names

$$\alpha \in \mathbf{P}$$

Security labels

$$\ell ::= \{\alpha_1 = l_1, \dots, \alpha_n = l_n\}$$

Essentially, an information security label  $\ell = \{\alpha_1 = l_1, \ldots, \alpha_n = l_n\}$  incorporates labels on various security properties about a piece of information: names  $\alpha_1, \ldots, \alpha_n$  from a name space  $\mathbf P$  identify the security properties, and  $l_i$  is the decentralized label on the property identified by  $\alpha_i$ . The security label  $\ell$  is composed of decentralized labels, but does not belong to the DLM itself. To distinguish these two kinds of labels, we call a decentralized label  $\ell$  a base label. The name space  $\mathbf P$  contains at least  $\ell$ ,  $\ell$  and  $\ell$  representing the confidentiality, integrity and availability properties, respectively. Label  $\ell$  usually has the form  $\ell$  and  $\ell$  are all time system, we may want to enforce timing integrity, which means that attackers cannot affect when a piece of data is generated. Then we can use the name  $\ell$  to represent the timing integrity property and specify a base label  $\ell$  on  $\ell$  to prevent attackers from compromising timing integrity under the assumption  $\ell$

Given a label  $\ell$ , let  $\alpha_i(\ell)$  denote the base label component corresponding to  $\alpha_i$ . For example,  $C(\ell)$ ,  $I(\ell)$ , and  $A(\ell)$  represent the respective confidentiality, integrity, and availability components of  $\ell$ .

It is convenient to have a single label to incorporate base labels on different properties. For example, this leads to a more succinct label constraint when analyzing information flows. An information flow from data  $d_1$  to data  $d_2$  means that the value of  $d_2$  may depend on the value of  $d_1$ . The security implications are that the confidentiality of  $d_1$  depends on the confidentiality of  $d_2$ , and the integrity of  $d_2$  depends on the integrity of  $d_1$ . Let  $\ell_1$  and  $\ell_2$  be the labels of  $d_1$  and  $d_2$ , respectively. The dependencies caused by the information flow impose the following label constraints:

$$C(\ell_1) \le C(\ell_2)$$

$I(\ell_2) \le I(\ell_1)$

Based on the two constraints, we can define an information flow ordering ( $\sqsubseteq$ ) on labels:

$$\frac{C(\ell_1) \le C(\ell_2)}{\ell_1 \sqsubseteq \ell_2} \frac{I(\ell_2) \le I(\ell_2)}{\ell_2}$$

Information flow from  $d_1$  to  $d_2$  is secure if and only if  $\ell_1 \sqsubseteq \ell_2$ . In addition, we can define a join ( $\sqcup$ ) operation on security labels: