# SOUND AND PRACTICAL METHODS FOR FULL-SYSTEM TIMING CHANNEL CONTROL

#### A Dissertation

Presented to the Faculty of the Graduate School of Cornell University

in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

by

Danfeng Zhang

August 2015

© 2015 Danfeng Zhang ALL RIGHTS RESERVED

## SOUND AND PRACTICAL METHODS FOR FULL-SYSTEM TIMING CHANNEL CONTROL

Danfeng Zhang, Ph.D.

#### Cornell University 2015

Building systems with rigorous security guarantees is difficult, because most programming languages lack support for reasoning about security. This situation is amplified by emerging timing attacks, which reveal secrets from computation time. Recent work shows that timing channels can quickly leak sensitive information, such as private keys of RSA and AES. Such threats greatly harm the security of many emerging applications, such as cloud computing, mobile computing, and embedded systems.

This dissertation describes novel programming languages and run-time enforcement mechanisms for full-system control of timing channels. The proposed approach has two major components: A new software-hardware security interface, and control mechanisms present at separate levels of system abstraction. These control mechanisms include:

- 1) A type system for an imperative language, so that well-typed programs provably leak only a bounded amount of information via timing channels,

- 2) SecVerilog, a hardware description language that supports mostly-static, precise reasoning about information flows in hardware designs, and

- 3) Predictive mitigation, a general run-time mechanism that permits tunable tradeoffs between security and performance.

Evaluation on real-world security-sensitive applications suggest that the proposed approach is sound and has reasonable performance.

#### **BIOGRAPHICAL SKETCH**

Danfeng Zhang was born in Suzhou, a beautiful city in China. He obtained his Bachelor/Master of Science degrees in Computer Science in 2006/2009 from Peking University in Beijing, China. Although his research back in China has little to do with programming languages and security, Danfeng was fascinated by the area of language-based security after entering Cornell University in 2009. Since then, he has been studying for his doctorate degree, with a focus on designing programming models with rigorous security guarantees and minimal burden on programmers.

To my family

#### **ACKNOWLEDGEMENTS**

Making this dissertation and my Ph.D. degree a reality is impossible without the help from many people. First and foremost, I want to thank my advisor Andrew Myers. He has been an incredible advisor in all dimensions, such as research, teaching, writing and presentation. Conversations with Andrew have always been educational and motivating. His high standard in research and teaching made him a role model for me.

I would like to thank the other members of my committee: Dexter Kozen and Bart Selman. I have benefited a lot from their teaching and talking to them about my research. Moreover, I am very grateful to G. Edward Suh, who has been a wonderful mentor whenever I encounter hardware-related questions.

During my six years at Cornell, many friends and fellow students have helped me in various ways. It is fortunate to start my first project with Aslan Askarov. His insights and feedbacks have helped to shape some of the ideas that this dissertation is built on. It is my great fortune to have Jed Liu, Michael George, Krishnaprasad Vikram, Owen Arden, Chinawat Isradisaikul, Tom Magrino, Yizhou Zhang, Isaac Sheff, Laure Thompson and Matthew Milano as colleagues. They have always been a reliable source for constructive feedbacks on research papers and presentations. I am also grateful to Yao Wang, Andrew Ferraiuolo and Rui Xu: I learnt so much about hardware designs and Verilog from them in the SecVerilog project.

The Ph.D. journey is mostly enjoyable, but is also sometimes painful. Last but not least, I wish to thank my family for being so supportive of my academic pursuits. To Mom and Dad, thank you for always being on my side since my childhood. To my wife, thank you for your accompany, understanding and sharing the joys and pains in these years.

## TABLE OF CONTENTS

| Biographical Sketch |                 |                                                            |    |  |  |

|---------------------|-----------------|------------------------------------------------------------|----|--|--|

|                     |                 | ication                                                    | iv |  |  |

|                     | Ack             | nowledgements                                              | V  |  |  |

|                     | Tabl            | e of Contents                                              | V  |  |  |

|                     | List            | of Tables                                                  | χ  |  |  |

|                     |                 | of Figures                                                 | X  |  |  |

| 1                   | Intr            | oduction                                                   | 1  |  |  |

|                     | 1.1             | Timing channel control: challenges                         | 4  |  |  |

|                     |                 | 1.1.1 Direct and indirect timing dependencies              | 4  |  |  |

|                     |                 | 1.1.2 Limitations of previous approaches                   | 5  |  |  |

|                     | 1.2             | Sound and practical full-system timing channel control     | 6  |  |  |

|                     |                 | 1.2.1 Hardware abstraction and assumptions                 | 7  |  |  |

|                     |                 | 1.2.2 Timing interface and software enforcements           | 8  |  |  |

|                     |                 | 1.2.3 Provably secure hardware design                      | 9  |  |  |

|                     |                 | 1.2.4 Quantitative control of timing channels              | 10 |  |  |

|                     | 1.3             | Outline                                                    | 12 |  |  |

| 2                   | Lan             | guage-Based Control and Mitigation of Timing Channels      | 14 |  |  |

|                     | 2.1             | Assumptions                                                | 14 |  |  |

|                     | 2.2             | A cross-domain timing interface                            | 15 |  |  |

|                     | 2.3             | A language for controlling timing channels                 | 16 |  |  |

|                     |                 | 2.3.1 Core semantics                                       | 17 |  |  |

|                     |                 | 2.3.2 Abstracted full language semantics                   | 18 |  |  |

|                     |                 | 2.3.3 Configurations                                       | 18 |  |  |

|                     |                 | 2.3.4 Threat model                                         | 19 |  |  |

|                     |                 | 2.3.5 Faithfulness requirements for the full semantics     | 21 |  |  |

|                     |                 | 2.3.6 Security requirements for the full semantics         | 23 |  |  |

|                     | 2.4             | A sketch of secure hardware                                | 26 |  |  |

|                     |                 | 2.4.1 Choosing machine environments                        | 26 |  |  |

|                     |                 | 2.4.2 Realization on standard hardware                     | 27 |  |  |

|                     |                 | 2.4.3 A more efficient realization                         | 29 |  |  |

|                     | 2.5             | A type system for controlling timing channels              | 30 |  |  |

|                     |                 | 2.5.1 Security type system                                 | 31 |  |  |

|                     |                 | 2.5.2 Machine-environment noninterference                  | 33 |  |  |

|                     | 2.6             | Related work                                               | 36 |  |  |

| 3                   | A F             | Hardware Design Language for Timing-Sensitive Information- |    |  |  |

| ,                   | Flow Security 3 |                                                            |    |  |  |

|                     | 3.1             | Background and approach                                    | 38 |  |  |

|                     |                 | 3.1.1 Information flow control in hardware                 | 38 |  |  |

|                     |                 | 3.1.2 Threat model                                         | 39 |  |  |

|   |      | 3.1.3   | Controlling timing channels in hardware   | . 40  |

|---|------|---------|-------------------------------------------|-------|

|   |      | 3.1.4   | Example: secure cache design              | . 41  |

|   |      | 3.1.5   | The SecVerilog approach                   | . 43  |

|   |      | 3.1.6   | Benefits over previous approaches         |       |

|   | 3.2  | SecVe   | erilog: Syntax and semantics              |       |

|   | 3.3  | SecVe   | erilog: Type system                       | . 47  |

|   |      | 3.3.1   | Type syntax                               |       |

|   |      | 3.3.2   | Typing rules                              |       |

|   |      | 3.3.3   | Mutable dependent security labels         |       |

|   |      | 3.3.4   | Constraints and hypotheses                | . 55  |

|   |      | 3.3.5   | Generating state predicates               |       |

|   |      | 3.3.6   | Discussion of typing rules                |       |

|   |      | 3.3.7   | Scalability of type checking              | . 59  |

|   |      | 3.3.8   | Well-formed typing environments           |       |

|   | 3.4  | Sound   | dness                                     | . 60  |

|   |      | 3.4.1   | Proving hardware properties from HDL code | . 60  |

|   |      | 3.4.2   | Observational determinism                 |       |

|   |      | 3.4.3   | Soundness of SecVerilog                   | . 62  |

|   | 3.5  | Sound   | dness proof                               | . 64  |

|   |      | 3.5.1   | Semantics                                 | . 64  |

|   |      | 3.5.2   | Typing rules                              | . 67  |

|   |      | 3.5.3   | Proofs                                    | . 68  |

|   | 3.6  | Relate  | ed work                                   | . 86  |

| 4 | Prec | dictive | Mitigation of Timing Channels             | 88    |

|   | 4.1  | Simpl   | le mitigation schemes                     |       |

|   |      | 4.1.1   | Black-Box system model                    | . 88  |

|   |      | 4.1.2   | Leakage measures                          |       |

|   |      | 4.1.3   | Quantizing time                           | . 91  |

|   |      | 4.1.4   | A basic mitigation scheme: fast doubling  | . 92  |

|   |      | 4.1.5   | Slow-doubling mitigation                  | . 94  |

|   | 4.2  | Genei   | ral epoch-based mitigation                | . 95  |

|   |      | 4.2.1   | Mitigation                                |       |

|   |      | 4.2.2   | Epoch-based mitigation                    |       |

|   |      | 4.2.3   | Leakage of epoch-based mitigators         | . 99  |

|   |      | 4.2.4   | Bounding leakage                          |       |

|   |      | 4.2.5   | Mixing storage and timing                 | . 104 |

|   |      | 4.2.6   | Input                                     | . 106 |

|   |      | 4.2.7   | Leakage with beliefs about execution time | . 106 |

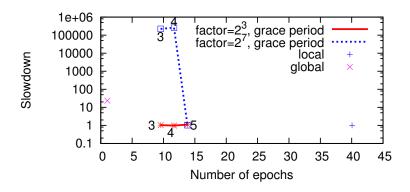

|   | 4.3  | Adap    | tive mitigation results                   | . 108 |

|   |      | 4.3.1   | Convergence                               | . 108 |

|   |      | 4.3.2   | Assumptions                               |       |

|   |      | 4.3.3   | An adaptive mitigation heuristic          | . 110 |

|   |      | 4.3.4   | Empirical results                         | 112   |

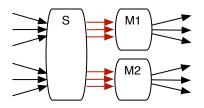

|   |      | 4.3.5    | Composing mitigators                                | 115 |

|---|------|----------|-----------------------------------------------------|-----|

|   | 4.4  | Applic   | cation-level experiments                            | 115 |

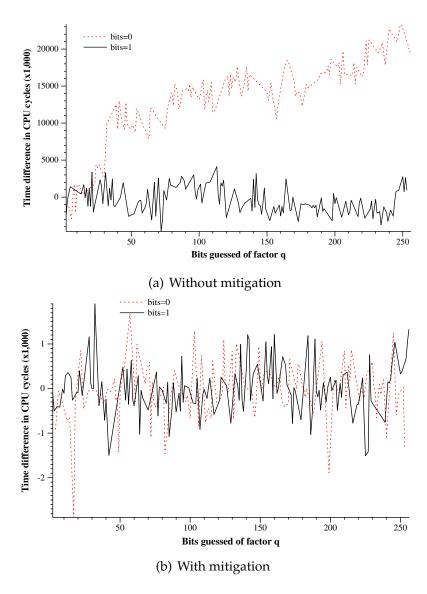

|   |      | 4.4.1    | RSA                                                 |     |

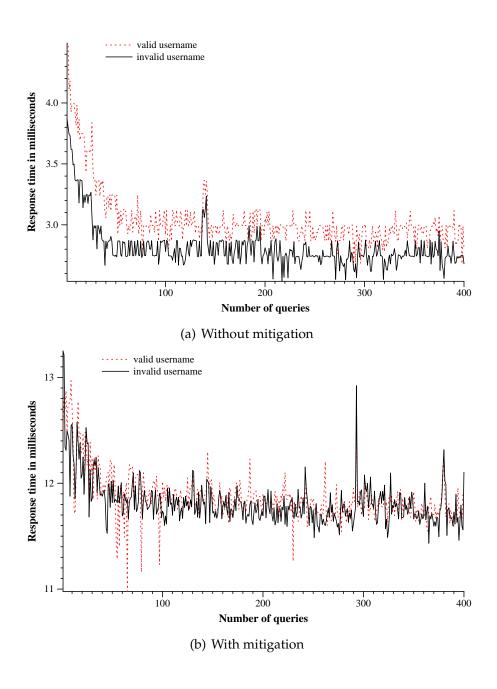

|   |      | 4.4.2    | Timing attacks on web servers                       | 119 |

|   | 4.5  | Genera   | alizing the black-box model for interactive systems |     |

|   | 4.6  |          | tions for interactive systems                       |     |

|   |      | 4.6.1    | •                                                   |     |

|   |      | 4.6.2    | Multiple input and output channels                  |     |

|   | 4.7  | Leakag   | ge analysis                                         |     |

|   |      | 4.7.1    |                                                     |     |

|   |      | 4.7.2    | <u> </u>                                            |     |

|   |      | 4.7.3    | 7 =                                                 |     |

|   |      | 4.7.4    | - · · · ·                                           |     |

|   |      | 4.7.5    | Security vs. performance                            |     |

|   |      | 4.7.6    | Leakage with a worst-case execution time            |     |

|   | 4.8  | Compo    | osing mitigators                                    |     |

|   | 4.9  |          | ments                                               |     |

|   |      | 4.9.1    | Mitigator design and its limitations                |     |

|   |      | 4.9.2    | Mitigator implementation                            |     |

|   |      | 4.9.3    | Leakage revisited                                   |     |

|   |      | 4.9.4    | Latency and throughput                              |     |

|   |      | 4.9.5    | Real-world applications with proxy                  | 158 |

|   | 4.10 | Related  | d work                                              |     |

| 5 | Land | 711200_F | Based Quantitative Control of Timing Channels       | 166 |

| 3 | 5.1  |          | guage with quantitative timing channel leakage      |     |

|   | 5.2  |          | itative properties of the type system               |     |

|   | 0.2  |          | Adversary observations                              |     |

|   |      | 5.2.2    | Measuring leakage in a multilevel environment       |     |

|   |      | 5.2.3    |                                                     |     |

|   | 5.3  |          | tive mitigation                                     |     |

|   | 0.0  | 5.3.1    | Mitigating semantics                                | 176 |

|   |      | 5.3.2    | Leakage analysis of the global policy               |     |

|   |      | 5.3.3    | Leakage analysis of the local policy                | 178 |

|   | 5.4  |          |                                                     | 180 |

|   | 0.1  | 5.4.1    | Extended language                                   | 180 |

|   |      | 5.4.2    | Notations                                           | 184 |

|   |      | 5.4.3    | Completeness of the extended language               | 184 |

|   |      | 5.4.4    | Useful lemmas                                       | 185 |

|   |      | 5.4.5    | Proof of timing properties                          |     |

|   |      |          | O 1 $-1$                                            |     |

| 6                                | Eva            | Evaluation |                                       |     |  |  |

|----------------------------------|----------------|------------|---------------------------------------|-----|--|--|

|                                  | 6.1            | Comp       | oilation                              | 205 |  |  |

| 6.2 Partitioned cache simulation |                |            |                                       | 206 |  |  |

|                                  |                | 6.2.1      | Web login case study                  | 207 |  |  |

|                                  |                | 6.2.2      | RSA case study                        | 209 |  |  |

|                                  | 6.3            | Forma      | ally verified MIPS processor          | 211 |  |  |

|                                  |                | 6.3.1      | A secure MIPS processor design        | 212 |  |  |

|                                  |                | 6.3.2      | Overhead of SecVerilog                | 214 |  |  |

|                                  |                | 6.3.3      | Overhead of timing channel protection | 216 |  |  |

| 7                                | Con            | clusio     | ns                                    | 220 |  |  |

| Bi                               | ibliography 22 |            |                                       |     |  |  |

## LIST OF TABLES

| 6.1 | Machine environment parameters                    | 206 |

|-----|---------------------------------------------------|-----|

| 6.2 | Login time with various options (in clock cycles) | 209 |

| 6.3 | Lines of Code (LOC) for each processor component  | 213 |

| 6.4 | Complete ISA of our MIPS processor                | 213 |

| 6.5 | Comparing processor designs                       | 217 |

## LIST OF FIGURES

| 2.1  | Syntax of the language                                                                                                                                   | 16  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2  | Core semantics of commands                                                                                                                               |     |

| 2.3  | Security requirements                                                                                                                                    | 23  |

| 2.4  | Typing rules: commands                                                                                                                                   | 31  |

| 3.1  | An example of full-system timing channel control. The well-typed program on the left is secure if the hardware enforces the security policy on the right | 40  |

| 3.2  | SecVerilog extends Verilog with security label annotations                                                                                               |     |

| 2.2  | (shaded in gray)                                                                                                                                         | 41  |

| 3.3  | Syntax of SecVerilog                                                                                                                                     | 45  |

| 3.4  | Syntax of security labels.                                                                                                                               | 47  |

| 3.5  | Typing rules: commands                                                                                                                                   | 48  |

| 3.6  | An example of implicit declassification                                                                                                                  | 50  |

| 3.7  | Dynamic erasure of contents                                                                                                                              | 51  |

| 3.8  | Examples illustrating the challenges of controlling label channels.                                                                                      |     |

| 3.9  | Predicate generation in Hoare logic                                                                                                                      | 57  |

| 3.10 | Small-step operational semantics of commands                                                                                                             | 65  |

| 3.11 | Small-step operational semantics of threads                                                                                                              | 65  |

| 3.12 | Typing rules: expressions                                                                                                                                | 68  |

| 3.13 | Typing rules: threads                                                                                                                                    | 68  |

| 3.14 | Big-step operational semantics of commands                                                                                                               | 69  |

| 3.15 | Big-step operational semantics of threads                                                                                                                | 69  |

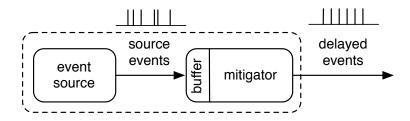

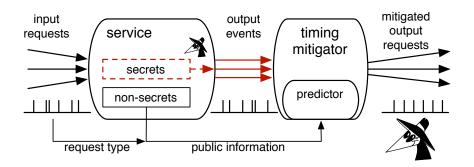

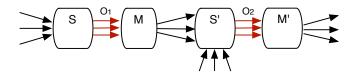

| 4.1  | System overview                                                                                                                                          | 88  |

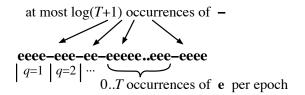

| 4.2  | Target bound, capacity approximation for individual epochs,                                                                                              |     |

|      | and deferral points                                                                                                                                      | 103 |

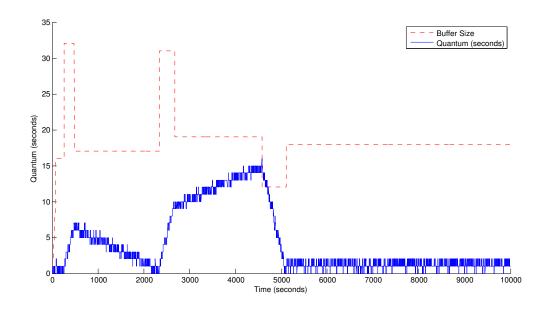

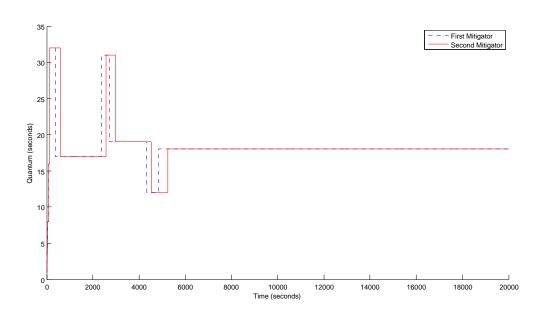

| 4.3  | Adaptive mitigation with average interval of 18 seconds                                                                                                  | 113 |

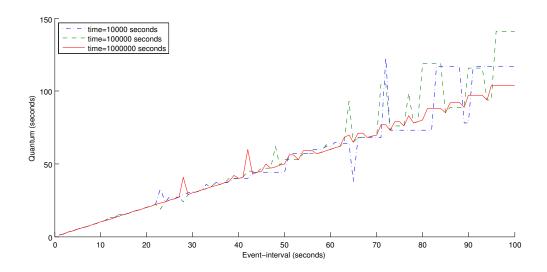

| 4.4  | Convergence with different event intervals                                                                                                               | 114 |

| 4.5  | Convergence of composition of mitigators with average interval                                                                                           | 11/ |

| 1.   | of 18 seconds.                                                                                                                                           |     |

| 4.6  | Simple mitigation of the RSA timing attack                                                                                                               |     |

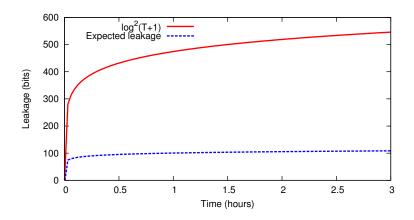

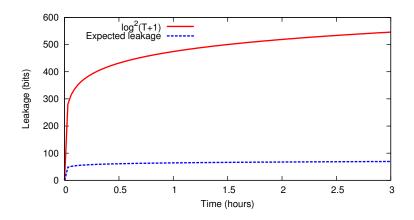

| 4.7  | Expected leakage for RSA timing channel attack                                                                                                           |     |

| 4.8  | Simple mitigation of the web server timing attack                                                                                                        |     |

| 4.9  | Expected leakage for web server timing attack                                                                                                            |     |

| 4.10 | Predictive mitigation of an interactive system                                                                                                           |     |

| 4.11 | Performance vs. security                                                                                                                                 |     |

| 4.12 | Parallel composition of mitigators                                                                                                                       |     |

| 4.13 | Sequential composition of mitigators                                                                                                                     |     |

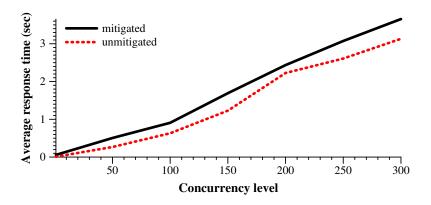

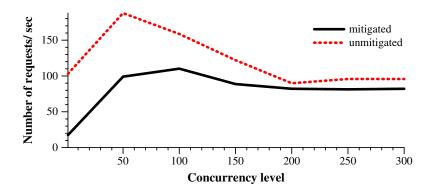

| 4.14 | Wiki latency with and without mitigation.                                                                                                                |     |

| 4.15 | Wiki throughput with and without mitigation                                                                                                              |     |

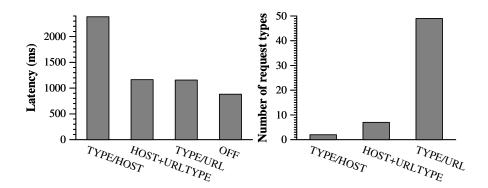

| 4.16 | Latency for an HTTP web page                                                                                                                             | 160 |

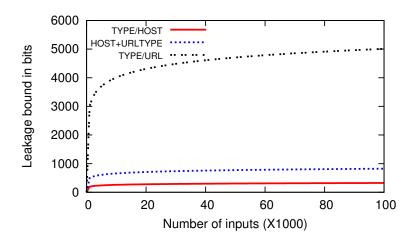

| Leakage bound for an HTTP web page                       | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

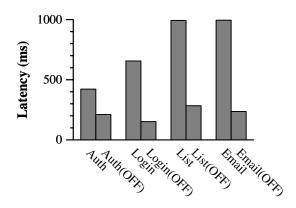

| Latency overhead for HTTPS webmail service               | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

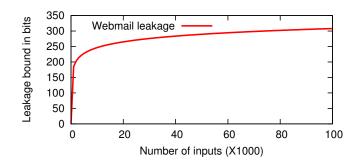

| Leakage bound for HTTPS webmail service                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Syntax of the full language with the mitigate command 10 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Core semantics of the mitigate command                   | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Typing rules: the mitigate command                       | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Quantitative leakage                                     | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Predictive semantics for mitigate                        | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Equivalence on memories and commands                     | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Extended syntax                                          | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Extended semantics of expressions                        | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Extended semantics of commands                           | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Typing rules: expressions                                | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Extended typing rules                                    | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

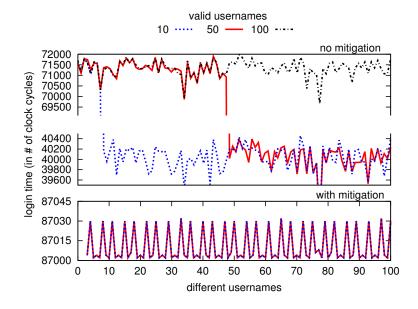

| Login time with various secrets                          | 09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

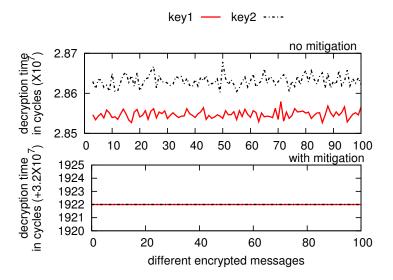

| Decryption time with various secrets                     | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

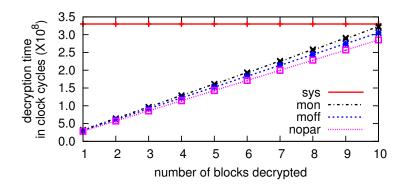

| Language-level vs. system-level mitigation               | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

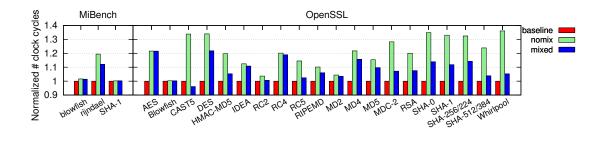

| Performance overhead of timing channel protection        | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                          | Latency overhead for HTTPS webmail service. 16 Leakage bound for HTTPS webmail service. 16 Syntax of the full language with the mitigate command. 16 Core semantics of the mitigate command. 16 Typing rules: the mitigate command. 16 Quantitative leakage. 17 Predictive semantics for mitigate. 17 Equivalence on memories and commands. 18 Extended syntax. 18 Extended semantics of expressions. 18 Extended semantics of commands. 18 Extended semantics of commands. 18 Extended typing rules: expressions. 18 Extended typing rules. 18 Login time with various secrets. 20 Decryption time with various secrets. 22 Language-level vs. system-level mitigation. 22 |

#### CHAPTER 1

#### **INTRODUCTION**

Timing channels have long been a difficult and important problem for computer security. The difficulty has long been recognized since the 70's [47, 26, 66], but their importance has been reinforced by recent work that shows timing channels can quickly leak sensitive information. Attacks exploit the timing of cryptographic operations [43, 13] and of web server responses [11]. These attacks work even without cooperation of any software on the system being timed. If the system contains malicious code or hardware (e.g., [74]), timing can also be exploited as a robust covert channel. Further, timing channels can be exploited stealthily, at low risk to the attacker [51].

Controlling timing channels is nevertheless extremely challenging, because confidential information can affect timing throughout the entire computer system. At the software level, a branch or loop conditioned on secret values creates timing channels. For instance, a branch condition depends on the private key in an early implementation of RSA, resulting in exploitable timing channels [43]. Moreover, even machine instructions with different operators can take variable time [18]. At the hardware level, shared hardware resources such as the data cache also creates timing channels. For example, cache probing attacks (e.g., [68, 65, 32]) exploit the timing channel that arises because accesses to memory locations by one process affect the cache, and thereby observably affect the timing behavior of later accesses by other processes. The cache is not the only problem. Attacks have also been shown that exploit timing channels arising from other components: instruction and data caches [2], branch predictors and branch target buffers [3], and shared functional units [87].

This dissertation introduces a sound and practical approach for full-system timing channel control. The core of this approach is a new software-hardware security interface, which for the first time, enables accurate reasoning about timing channels at the software-language level. Unlike previous work on language-based timing channel control, such as code transformation [4], this interface supports more realistic programs and hardware. For example, it can be implemented on hardware with an instruction cache, branch predictors, shared functional units, and so on. Such a new security interface forms a rigorous security contract between the software (language) level and the hardware implementation, enabling provable control of timing channels throughout the entire computer system.

On the software side, this dissertation presents a type system that provides fine-grained reasoning about timing channels, assuming the hardware follows the security contract. The type system can distinguish between benign timing variations and those carrying confidential information, and can distinguish between multiple distinct security levels. This fine-grained reasoning about timing channels improves the tradeoff between security and performance: benign timing variations provably leak no confidential information, so only the timing of code fragments that carry confidential information needs to be controlled.

On the hardware side, the security contract is formalized into three security requirements, guiding secure hardware designs. To formally verify such secure designs, this dissertation presents SecVerilog, a new hardware design language that statically checks information flows within hardware, including flows via timing channels. Unlike previous approaches, SecVerilog enables flexible, finegrained reuse and sharing of hardware across security domains, via a novel type

system with dependent types. The benefit is that almost no additional run-time overhead is added, since SecVerilog checks information flows at compile time; little chip area and energy consumption is added since hardware resources can be shared securely across security domains.

To control timing channels arising from code fragments that do leak information, this dissertation proposes predictive mitigation, a practical method for a broad class of computing systems. Unlike previous general techniques for timing channel mitigation, this framework offers tunable tradeoffs between security and performance, so that programmers may improve system performance with a programmer-specified leakage function. By incorporating mechanisms for predictive mitigation of timing channels, the aforementioned software-level type system can also permit an expressive programming model, where applications with a provably bounded amount of timing leakage are allowed.

The soundness and effectiveness of the proposed approach are demonstrated on applications previously shown to be vulnerable to timing attacks, as well as security benchmarks. A complete MIPS processor with modern processor features, such as data hazard detection and data bypassing, is formally verified in SecVerilog. The results suggest that the combination of language-based mitigation and secure hardware works well, with overheads of only 1% in chip area, critical path delay and power consumption. Moreover, performance overhead for the verified applications running on the verified processor is about 20% on average .

#### 1.1 Timing channel control: challenges

Timing channels are perhaps the most challenging aspect of information flow security, because confidential information can affect timing in various ways: at the software level, a branch or loop conditioned on secret values creates timing channels [43]; at the hardware level, shared hardware resources such as the data cache also create timing channels [68, 65, 18, 32].

#### 1.1.1 Direct and indirect timing dependencies

We first define *direct* and *indirect* timing dependencies to distinguish timing channels arising from software and hardware respectively. We call timing channels visible at the source-language level *direct timing dependencies*. In the following example, control flow affects timing.

```

1 if (h)

2 sleep(1);

3 else

4 sleep(10);

5 sleep(h);

```

Assume h holds confidential data and that sleep (*e*) suspends execution of the program for the amount of time specified by *e*. Since line 4 takes longer to execute than line 2, one bit of h is leaked through timing. Such control-flow-related timing channels are real issues in practice, as demonstrated by attacks on RSA [43, 13]. Another source of direct timing dependencies is operations whose execution time depends on parameter values, such as the sleep command at line 5. In general, even machine instructions can take variable time [18].

Modern hardware also creates *indirect timing dependencies* in which execution time depends on hardware state that has no source-level representation. The following code shows that the data cache is one source of indirect dependencies.

```

1 if (h1)

2 h2:=11;

3 else

4 h2:=12;

5 13:=11;

```

Suppose only h1 and h2 are confidential and that neither 11 nor 12 are cached initially. Even though both branches have the same instructions and similar memory access patterns, executing this code fragment is likely to take less time when h1 is not zero: because 11 is cached at line 2, line 5 runs faster, and the value of h1 leaks through timing.

Some timing attacks [65, 32] exploit data cache timing dependencies to infer AES encryption keys, but indirect dependencies arising from other hardware components have also been exploited to construct attacks: instruction and data caches [2], branch predictors and branch target buffers [3], and shared functional units [87].

## 1.1.2 Limitations of previous approaches

Due to the existence of indirect timing dependencies, software-based solutions are doomed to fail. Much prior language-based work uses simple, implicit models of timing, and no previous work fully addresses indirect dependencies. For example, type systems have been proposed to prevent timing channels, but are very restrictive. Often (e.g., [86, 78, 73, 76]) timing behavior of the program is assumed to be accurately described by the number of steps taken in an opera-

tional semantics. This assumption does not hold even at the machine-language level. As a result, these prior methods fail to handle timing channels arising from hardware features, such as data cache.

Some previous work uses program transformation to remove indirect dependencies, though only those arising from the data cache. The main idea is to equalize the execution time of different branches, but a price is paid in expressiveness, since these languages either rule out loops with confidential guards (as in [4, 34, 10]), or limit the number of loop iterations (as in [56, 18]). Moreover, these methods do not handle all indirect timing dependencies; for example, the instruction cache is not handled, so verified programs remain vulnerable to other indirect timing attacks [87, 3, 2].

Recent work in the architecture community has aimed for hardware-based solutions to timing channels. Their hardware designs implicitly rely on assumptions about how software uses the secure hardware, but these assumptions have not been rigorously defined or formally verified. For example, the cache design by Wang and Lee [88] works only under the assumption that the AES lookup table is preloaded into the cache and that the load time is not observable to the adversary [44].

#### 1.2 Sound and practical full-system timing channel control

Timing channels cannot be controlled effectively at the software level only. Hardware mechanisms can help, but do a poor job of controlling language-level leaks such as direct timing dependencies. The question, then, is how to usefully and accurately characterize the timing semantics of code at the source level. Our

insight is to combine the language-level and hardware-level mechanisms, via a new cross-domain interface.

#### 1.2.1 Hardware abstraction and assumptions

Throughout this dissertation, we use the term *machine environment* to refer to all hardware state that is invisible at the language level but that is needed to predict timing. Timing channels relying on indirect dependencies are at best difficult to reason about at the language level—the semantics of programming languages and even of instruction set architectures (ISAs) hide information about execution time by abstracting away low-level implementation details. For instance, it is difficult to reason about timing without knowing how the data cache works.

We assume all (software-level) information is associated with a *security label*, describing the confidentiality of the information. Labels  $\ell_1$  and  $\ell_2$  are ordered, written  $\ell_1 \sqsubseteq \ell_2$ , if  $\ell_2$  describes a confidentiality requirement that is at least as strong as that of  $\ell_1$ . It is secure for information to flow from label  $\ell_1$  to label  $\ell_2$  if  $\ell_1 \sqsubseteq \ell_2$ . We assume there are at least two distinct labels L (low) and H (high) such that L  $\sqsubseteq$  H and H  $\not\sqsubseteq$  L. The label of public information is L; that of secret information is H.

Accordingly, we can logically partition the machine environment according to the security labels associated with hardware state. For example, a commodity cache with no partition is a special case where all cache lines are associated with the same label. In general, different partitions in a partitioned cache [88] can be associated with different labels. For hardware components such as a pipeline, we can time-multiplex their use according to different security labels.

#### 1.2.2 Timing interface and software enforcements

To concisely track how the machine environment affects timing, and how information flows into the machine environment, we propose a new cross-domain timing interface, in form of two *timing labels*. In particular, we associate two timing labels with each command in the program. The first of these labels is the command's *read label*  $\ell_r$ . The read label is an upper bound on the label of machine environment that affects the run time of the command. For example, the run time of a command with  $\ell_r = L$  depends only on cache state with label L or below. The second of these labels is the command's *write label*  $\ell_w$ . The write label is a lower bound on the label of machine environment that the command can modify. It ensures that the labels of machine environment reflect the confidentiality of information that has flowed into that machine environment.

For example, suppose that there is only one (low) data cache, which to be conservative means that anyone can learn from timing whether a given memory location is cached. Therefore, both the read and write label of every command must be L. The example in Section 1.1.1 is then annotated as follows, where the first label in brackets is the read label, and the second, the write label.

```

if (h1)<sub>[L,L]</sub>

h2:=11;<sub>[L,L]</sub>

else

h2:=12;<sub>[L,L]</sub>

13:=11;<sub>[L,L]</sub>

```

This example is insecure because execution of lines 2 and 4 is conditioned on the high variable h1. Therefore these lines are in a *high context*, one in which the program counter label [21] is high. If lines 2 and 4 update cache state in the usual way, the low write label permits low hardware state to be affected by h1.

This insecure information flow is a form of *implicit flow* [21], but one in which hardware state with no language-level representation is being updated.

Since lines 2 and 4 occur in a high context, the write label of these commands must be H for this program to be secure. Consequently, the hardware may not update low parts of the machine environment. One way to avoid modifying the low parts of a commodity cache is to deactivate it in high contexts, since the entire cache is low. A generalization of this idea is to use a partitioned cache, where different partitions are associated with different labels. In this case, cache misses in a high context then cause only the high cache partition to be updated.

With the read and write labels abstracting the timing behavior of hardware, timing channel security can be statically checked at the language level, according to the type system described in Chapter 2. Moreover, these timing labels could be inferred automatically according to the type system, reducing the burden on programmers.

## 1.2.3 Provably secure hardware design

The aforementioned cross-domain interface (read and write labels) communicates information flows between the software and hardware, enabling timing channels to be rigorously controlled. The interface defines a contract that both software and hardware must follow for their composition to correctly control information flows. The next question is how to design complex hardware that correctly enforces its part of the contract.

To provide provable security for hardware designs, Chapter 3 presents a

method for designing hardware that correctly, precisely, and efficiently enforces secure information flow. This method is based on a new hardware description language (HDL) called SecVerilog, which adds a security type system to Verilog so that hardware-level information flows can be checked statically. In combination with software-level information flow control, our hardware design method enables building computing systems in which all forms of information flow are tracked, including implicit flows and timing channels.

SecVerilog has several advantages over the state of the art in secure hardware design. SecVerilog checks information flows statically while providing formal security assurance and guidance to hardware designers, avoiding runtime costs of tracking and checking of information flow. The language is expressive enough to prove security of a design even when hardware resources are shared among multiple security levels that are changed at a per-cycle granularity, avoiding the duplication of hardware resources. The novel dependent type system of SecVerilog follows a modular design that decouples the program analyses required for precision from the type system, making it more amenable to future extension. Our prototype secure pipelined MIPS processor with a cache adds area and clock cycle overheads of only about 1%.

## 1.2.4 Quantitative control of timing channels

Strictly disallowing all timing leakage can be done as sketched thus far, but results in an impractically restrictive programming language, or computer system, because execution time is prevented from depending on confidential information in any way.

To provide a strict bound on timing channel leakage while providing practical performance, Chapter 4 introduces a general framework called *predictive mitigation*. The key idea is that given a prediction of how long a computation will take, solely based on public information, a run-time enforcement can ensure that at least that much time is consumed by simply waiting if necessary. In the case of a misprediction (i.e., when the estimate is too low), a larger prediction is generated, and the execution time is padded accordingly. Mispredictions also inflate the predictions generated by subsequent mitigated computation, so that the total timing leakage is tightly bounded.

Predictive mitigation bounds the amount of information leaked through the timing channel as a function of elapsed time. Simple mitigation schemes can ensure that no more than  $\log^2(T)$  bits of information are leaked, where T is the running time (all logarithms in this dissertation are base 2). Further, an arbitrary bound on information leakage can be enforced. However, tighter bounds have a price: they can reduce system throughput and increase system latency, particularly if the system has unpredictable behavior.

Chapter 5 incorporates the predictive mitigation framework into the software language in Chapter 2 by a new command called mitigate. Command (mitigate  $(e,\ell)$  c) executes the command c while ensuring that timing leakage is bounded. Here, the expression e computes an initial prediction for the execution time of c. The label  $\ell$  bounds what information can be learned by observing the timing leakage c. That is, no information at level  $\ell'$  such that  $\ell' \not\sqsubseteq \ell$  can be learned from c's execution time.

#### 1.3 Outline

This dissertation presents and explores practical methods for full-system timing channel control. The key component, a cross-domain timing interface that enables compositional enforcement, is presented in Chapter 2. Chapter 2 also includes formal restrictions that are required by the interface on hardware implementation, as well as how the timing interface enables a software-level type system that provably eliminates all timing channels, with the assumption that hardware respects the interface.

Chapter 3 introduces the SecVerilog language, which extends Verilog with expressive type annotations that enable precise reasoning about information flow. The language also comes with rigorous formal assurance: SecVerilog provably enforces timing-sensitive noninterference and thus ensures secure information flow.

Chapter 4 describes a general framework, called predictive mitigation, which provides provable tight timing-channel leakage bound for applications where a limited leakage is allowed. We start from a black-box model, where we know nothing about a system other than the output events, and then extend it to interactive systems, which receive input requests from multiple clients and deliver responses.

Chapter 5 incorporates the predictive mitigation framework (Chapter 4) into the software language introduced in Chapter 2. The result is an expressive programming model, where applications with a provably bounded amount of timing leakage are allowed.

The soundness and effectiveness of the approach proposed in this dissertation is demonstrated on real-world security-sensitive applications, in Chapter 6. The results suggest this approach controls timing channels, and has reasonable performance for these real-world applications. Chapter 7 summarizes.

The materials presented in Chapters 2, 4 and 5 are adapted from joint work with Aslan Askarov and Andrew Myers [95, 6, 94]. Chapter 3, the SecVerilog language, is adapted from joint work with Yao Wang, G. Edward Suh and Andrew Myers [96].

#### **CHAPTER 2**

## LANGUAGE-BASED CONTROL AND MITIGATION OF TIMING CHANNELS

Timing channels have long been a difficult and important problem for computer security. They can be used by adversaries as side channels or as covert channels to learn private information, including cryptographic keys and passwords.

This chapter introduces a complete and effective language-based method for controlling timing channels. An important contribution of this chapter is a system of simple, static annotations that provides just enough information about the underlying language implementation to enable accurate reasoning about timing channels. These annotations form a contract (formalized in this chapter) between the software (language) level and the hardware implementation. We design a novel type system based on the annotations, and formally prove that any well-typed program has no timing channel leakage, assuming that the hardware implementation obeys the contract.

## 2.1 Assumptions

Recall that throughout this dissertation, we follow the terms and assumptions defined in Section 1.2.1. We use the term *machine environment* to refer to all hardware state that is invisible at the language level but that is needed to predict timing. Examples include the compiler, operating system, data cache, instruction cache, and so on. We assume all software-level information and all components of the machine environment are associated with *security labels*, describing the

corresponding confidentiality. As a special case, commodity cache with no partition has all cache lines associated with the same label. In general, different partitions in a partitioned cache [88] can be associated with different labels. For hardware components such as a pipeline, we can time-multiplex the use of them according to different security labels.

#### 2.2 A cross-domain timing interface

The syntax and semantics of programming languages and even of instruction set architectures (ISAs) intentionally hide information about execution time by abstracting away low-level implementation details. Doing so is beneficial for simpler reasoning about non-timing-related software properties, as well as for portability. But on the other hand, hiding timing information also makes it at best difficult to reason about timing channels arising from hardware features, such as the data cache, at the language level.

To track how information flows into the machine environment, but without concretely representing the hardware state, we propose a novel cross-domain interface in this dissertation. This interface consists of two labels with each command in the program. The first of these labels is the command's *read label*  $\ell_r$ . The read label is an upper bound on the label of hardware state that affects the run time of the command. For example, the run time of a command with  $\ell_r = L$  depends only on hardware state with label L or below. The second of these labels is the command's *write label*  $\ell_w$ . The write label is a lower bound on the label of hardware state that the command can modify. For example, no machine environment with a label H can be modified during the execution of a command with  $\ell_r = L$ .

```

e ::= n \mid x \mid e \text{ op } e

c ::= \text{skip}_{[\ell_r, \ell_w]} \mid (x := e)_{[\ell_r, \ell_w]} \mid c; c \mid (\text{while } e \text{ do } c)_{[\ell_r, \ell_w]}

\mid (\text{if } e \text{ then } c_1 \text{ else } c_2)_{[\ell_r, \ell_w]} \mid (\text{sleep } e)_{[\ell_r, \ell_w]}

```

Figure 2.1: Syntax of the language.

Next, we introduce a core language with read and write labels. Formal definition and semantics of these labels are deferred to Section 2.3.6.

## 2.3 A language for controlling timing channels

Figure 2.1 gives the syntax for an imperative language with timing channel control. The novel elements—read and write labels—have already been introduced. Notice that the sequential composition command itself needs no timing labels. The syntax is mostly standard: it has assignments, sequential compositions, loops and branches. Command ( $sleep\ e$ ) suspends execution of the program for the amount of time specified by e.

We present our semantics in a series of modular steps. We start with a *core* semantics, a largely standard semantics for a simple while-language, which ignores timing. Next, we develop an abstracted full semantics that describes the timing semantics of the language more accurately while abstracting away parameters that depend on the language implementation, including the hardware and the compiler.

$$\langle \operatorname{skip}_{[\ell_r,\ell_w]},m\rangle \to \langle \operatorname{stop},m\rangle \qquad \langle (\operatorname{sleep} e)_{[\ell_r,\ell_w]},m\rangle \to \langle \operatorname{stop},m\rangle$$

$$\frac{\langle c_1,m\rangle \to \langle \operatorname{stop},m'\rangle}{\langle c_1;c_2,m\rangle \to \langle c_2,m'\rangle} \qquad \frac{\langle c_1,m\rangle \to \langle c_1',m'\rangle \quad c_1' \neq \operatorname{stop}}{\langle c_1;c_2,m\rangle \to \langle c_1';c_2,m'\rangle}$$

$$\frac{\langle e,m\rangle \Downarrow v}{\langle (x:=e)_{[\ell_r,\ell_w]},m\rangle \to \langle \operatorname{stop},m[x\mapsto v]\rangle}$$

$$\frac{\langle e,m\rangle \Downarrow n \quad n\neq 0 \implies i=1 \quad n=0 \implies i=2}{\langle (\operatorname{if} e \operatorname{then} c_1 \operatorname{else} c_2)_{[\ell_r,\ell_w]},m\rangle \to \langle c_i,m\rangle}$$

$$\frac{\langle e,m\rangle \Downarrow n \quad n\neq 0}{\langle (\operatorname{while} e \operatorname{do} c)_{[\ell_r,\ell_w]},m\rangle \to \langle c;(\operatorname{while} e \operatorname{do} c)_{[\ell_r,\ell_w]},m\rangle}$$

$$\frac{\langle e,m\rangle \Downarrow n \quad n=0}{\langle (\operatorname{while} e \operatorname{do} c)_{[\ell_r,\ell_w]},m\rangle \to \langle \operatorname{stop},m\rangle}$$

Figure 2.2: Core semantics of commands.

#### 2.3.1 Core semantics

For expressions we use a standard big-step evaluation  $\langle e,m\rangle \Downarrow v$  when expression e in memory m evaluates to value v. For commands (Figure 2.2), we write  $\langle c,m\rangle \to \langle c',m'\rangle$  for the transition of command c in memory m to command c' in memory m'. Note that read and write labels are not used in these rules. The rules use stop as a syntactic marker of the end of computation. We distinguish stop from the command  $\operatorname{skip}_{[\ell_r,\ell_w]}$  because  $\operatorname{skip}$  is a real command that may consume some measurable time (e.g., reading from the instruction cache), whereas stop is purely syntactic and takes no time at all. Since time is not part of the core semantics, sleep behaves like  $\operatorname{skip}$ .

#### 2.3.2 Abstracted full language semantics

The core semantics discussed so far ignores timing; the job of the full language semantics is to supply a complete description of timing so that timing channels can be precisely identified.

Writing down a full semantics as a set of transition rules would define the complete timing behavior of the language. But this semantics would be useful only for a particular language implementation on particular hardware. Instead, we permit *any* full semantics that satisfies a certain set of properties yet to be described. What is presented here is therefore a kind of abstracted full semantics in which only the key properties are fixed. This approach makes the results more general.

These key properties fall into two categories, which we call *faithfulness* requirements and security requirements. The faithfulness requirements (Section 2.3.5) are mostly straightforward; the security requirements (Section 2.3.6) are more subtle.

#### 2.3.3 Configurations

Configurations in the full semantics have the form  $\langle c, m, E, G \rangle$ . As in the core semantics, c and m are the current program and memory. Component E is the machine environment, and G is the global clock. In general G can be measured in any units of time, but we interpret it as machine clock cycles hereafter. We write  $\langle c, m, E, G \rangle \rightarrow \langle c', m', E', G' \rangle$  for evaluation transitions.

The full semantics of expression evaluation obviously also needs to be small-

step, but we choose a presentation style that elides the details of expression evaluation for simplicity.

As before, the machine environment E represents hardware state that may affect timing but that is not needed by the core semantics. Hardware components captured by E include the data cache and instruction cache, the branch prediction buffer, the translation lookaside buffer (TLB), and other low-level components. The machine environment might also include hidden state added by the compiler for performance optimization.

For example, if one considers only the timing effects of data and instruction caches, denoted by D and I respectively, E could be a configuration of the form  $E = \langle D, I \rangle$ .

Note that while both the memory m and the machine environment E can affect timing, only the memory affects program control flow. This is the reason to distinguish them in the semantics. The environment E can be completely abstract as long as the properties for the full semantics are satisfied. This separation also ensures that the core semantics is completely standard.

The separation of m and E also clarifies possibilities for hardware design. For instance, it is possible for confidential data to be stored securely in a public partition of E, but not in public memory (cf. Section 2.4.1).

#### 2.3.4 Threat model

To evaluate whether the programming language achieves its security goals, we need to describe the power of the adversary in terms of the semantics. We as-

sociate an adversary with a security level  $\ell_A$  bounding what information the adversary can observe directly. To represent the confidentiality of memory, we assume that an environment  $\Gamma$  maps variable names to security levels. If a memory location (variable) has security level  $\ell$  that flows to  $\ell_A$  (that is,  $\ell \sqsubseteq \ell_A$ ), the adversary is able to see the contents of that memory location. By monitoring such a memory location for changes, the adversary can also measure the times at which the location is updated.

Two memories  $m_1$  and  $m_2$  are  $\ell$ -equivalent, denoted  $m_1 \sim_{\ell} m_2$ , when they agree on the contents of locations at level  $\ell$  and below:

$$m_1 \sim_{\ell} m_2 \triangleq \forall x . \Gamma(x) \sqsubseteq \ell . m_1(x) = m_2(x)$$

Intuitively,  $\ell$ -equivalence of two memories means that an observer at level  $\ell$  cannot distinguish these two memories.

**Projected equivalence** We define *projected equivalence* on memories to require equivalence of variables with *exactly* level  $\ell$ :

$$m_1 \simeq_{\ell} m_2 \triangleq \forall x \cdot \Gamma(x) = \ell \cdot m_1(x) = m_2(x)$$

We assume there is a corresponding projected equivalence relation on machine environments. If two machine environments  $E_1$  and  $E_2$  have equivalent  $\ell$ -projections, denoted  $E_1 \simeq_{\ell} E_2$ , then  $\ell$ -level information that is stored in these environments is indistinguishable. The precise definition of projected equivalence depends on the hardware and perhaps the language implementation. For example, for a two-level partitioned cache containing some entries at level L and some at level H, two caches have equivalent H-projections if they contain the same cache entries in the H portion, regardless of the L entries.

Using projected equivalence it is straightforward to define  $\ell$ -equivalence on machine environments:

$$E_1 \sim_{\ell} E_2 \triangleq \forall \ell' \sqsubseteq \ell \cdot E_1 \simeq_{\ell'} E_2$$

## 2.3.5 Faithfulness requirements for the full semantics

The faithfulness requirements for the full semantics comprise four properties: adequacy, deterministic execution, sequential composition, as well as accurate sleep duration.

Adequacy specifies that the core semantics and the full semantics describe the same executions: for any transition in the core semantics there is a matching transition in the full semantics and vice versa.

**Property 1 (Adequacy of core semantics)**  $\forall m, c, c', E, G$ .

$$(\exists E', G' . \langle c, m, E, G \rangle \to \langle c', m', E', G' \rangle) \Leftrightarrow \langle c, m \rangle \to \langle c', m' \rangle$$

We also require that the full semantics be deterministic, which means that the machine environment *E* completely captures the possible influences on timing.

**Property 2 (Deterministic execution)**  $\forall m, c, E, G$ .

$$\langle c, m, E, G \rangle \rightarrow \langle c_1, m_1, E_1, G_1 \rangle \land \langle c, m, E, G \rangle \rightarrow \langle c_2, m_2, E_2, G_2 \rangle \implies E_1 = E_2 \land G_1 = G_2$$

Since the core semantics is already deterministic, determinism of the machine environment and time components suffices.

Sequential composition must correctly accumulate time and propagate the machine environment.

#### **Property 3 (Sequential composition)**

1.

$$\forall c_1, c_2, m, E, G$$

.

$\langle c_1, m, E, G \rangle \rightarrow \langle \text{stop}, m', E', G' \rangle \Leftrightarrow \langle c_1; c_2, m, E, G \rangle \rightarrow \langle c_2, m', E', G' \rangle$

2.

$$\forall c_1, c_2, c'_1, m, E, G \text{ such that } c'_1 \neq \text{stop}$$

.

$\langle c_1, m, E, G \rangle \rightarrow \langle c'_1, m', E', G' \rangle \Leftrightarrow \langle c_1; c_2, m, E, G \rangle \rightarrow \langle c'_1; c_2, m', E', G' \rangle$

Finally, the sleep command must take the correct amount of time. When its argument is negative, it is assumed to take no time.

**Property 4 (Accurate sleep duration)**  $\forall n, m, E, G, \ell_r, \ell_w$ .

$$\langle (\mathtt{sleep} \ n)_{[\ell_r,\ell_w]}, m, E, G \rangle \rightarrow \langle \mathtt{stop}, m, E', G' \rangle \Rightarrow G' = G + \max(n, 0)$$

**Discussion** The faithfulness requirements are mostly straightforward. The assumption of determinacy might sound unrealistic for concurrent execution. But if information leaks through timing because some other thread preempts this one, the problem is in the scheduler or in the other thread, not in the current thread. Deterministic time is realistic if we interpret G as the number of clock cycles the current thread has used.

**Property 5 (Write label)** Given a labeled command  $c_{[\ell_r,\ell_w]}$ , and a level  $\ell$  such that  $\ell_w \not\sqsubseteq \ell$

$$\forall m, E, G : \langle c_{[\ell_r, \ell_w]}, m, E, G \rangle \to \langle c', m', E', G' \rangle \implies E \simeq_{\ell} E'$$

**Property 6 (Read label)** Given any command  $c_{[\ell_r,\ell_w]}$ ,

$$\forall m_1, m_2, E_1, E_2, G : (\forall x \in \mathbf{Vars}_1(c_{[\ell_r, \ell_w]}) : m_1(x) = m_2(x))$$

$$\land E_1 \sim_{\ell_r} E_2$$

$$\land \langle c_{[\ell_r, \ell_w]}, m_1, E_1, G \rangle \rightarrow \langle c_1, m_1', E_1', G_1 \rangle$$

$$\land \langle c_{[\ell_r, \ell_w]}, m_2, E_2, G \rangle \rightarrow \langle c_2, m_2', E_2', G_2 \rangle \implies G_1 = G_2$$

**Property 7 (Single-step machine-environment noninterference)** *Given any labeled command*  $c_{[\ell_r,\ell_w]}$ , and any level  $\ell$ ,

$$\forall m_1, m_2, E_1, E_2, G_1, G_2 . m_1 \sim_{\ell} m_2 \wedge E_1 \sim_{\ell} E_2$$

$$\wedge \langle c_{[\ell_r, \ell_w]}, m_1, E_1, G_1 \rangle \rightarrow \langle c_1, m_1', E_1', G_1' \rangle$$

$$\wedge \langle c_{[\ell_r, \ell_w]}, m_2, E_2, G_2 \rangle \rightarrow \langle c_2, m_2', E_2', G_2' \rangle \implies E_1' \sim_{\ell} E_2'$$

Figure 2.3: Security requirements.

## 2.3.6 Security requirements for the full semantics

For security, the full semantics also must satisfy certain properties to ensure that read and write labels accurately describe timing. These properties are specified as constraints on the full semantics that must hold after each evaluation step. In the formalization of these properties, we quantify over labeled commands with the form  $c_{[\ell_r,\ell_w]}$ : that is, all commands except sequential composition.

Write labels The write label  $\ell_w$  is the lower bound on the parts of the machine environment that a single evaluation step modifies. Property 5 in Figure 2.3 formalizes the requirements on the machine environment: executing a labeled command  $c_{[\ell_r,\ell_w]}$  cannot modify parts of the environment at levels to which  $\ell_w$  does not flow.

**Example** Consider program  $sleep(h)_{[\ell_r,H]}$  under the two-level security lattice  $L \sqsubseteq H$ . This command is annotated with the write label H. The only level  $\ell$  such that  $\ell_w \not\sqsubseteq \ell$  is  $\ell = L$ . In this case, Property 5 requires that an execution of  $sleep(h)_{[\ell_r,H]}$  does not modify L parts of the machine environment.

Consider program  $sleep(h)_{[\ell_r,L]}$  which has write label L. Because there is no security level  $\ell$  such that L  $\not\sqsubseteq \ell$ , Property 5 does not constrain the machine environment for this command.

**Read labels** The read label  $\ell_r$  of a command specifies which parts of the machine environment may affect the time necessary to perform the single next evaluation step. For a compound command such as if or while, this time does not include time spent in subcommands.

Property 6 in Figure 2.3 formalizes the requirement that read labels accurately capture the influences of the machine environment. This formalization uses the  $\mathbf{Vars}_1$  function, which identifies the part of memory that may affect the timing of the next evaluation step—that is, a set of variables. We need  $\mathbf{Vars}_1$  because parts of the memory can also affect timing, such as e in sleep (e). A simple syntactic definition of  $\mathbf{Vars}_1$  conservatively approximates the timing influences of memory, but a more precise definition might depend on particularities of the hardware implementation. For skip, this set is empty; for x := e and sleep (e), the set consists of x and all variables in expression e; for if e then e0 then e1 else e2 and while e do e2, it contains only variables in e3 and excludes those in subcommands, since only e3 is evaluated during the next step.

In the definition in Figure 2.3, equality of  $G_1$  and  $G_2$  means that a single step takes exactly the same time. Both configurations take the same time, because

$m_1$  and  $m_2$  must agree on all variables x that are evaluated in this step. This expresses our assumption that values of variables other than those explicitly evaluated in a single step cannot influence its timing. Machine environments  $E_1$  and  $E_2$  are required to be  $\ell_r$ -equivalent, to ensure that parts of the machine environment other than those at  $\ell_r$  and below also cannot influence its timing.