# Fast Evaluation of S-boxes with Garbled Circuits

Erik Pohle, Aysajan Abidin, Bart Preneel

Abstract-Garbling schemes are vital primitives for privacypreserving protocols and secure two-party computation. This paper presents a projective garbling scheme that assigns  $2^n$ values to wires in a circuit comprising XOR and unary projection gates. A generalization of FreeXOR allows the XOR of wires with  $2^n$  values to be very efficient. We then analyze the performance of our scheme by evaluating substitution-permutation ciphers. Using our proposal, we measure high-speed evaluation of the ciphers with a moderately increased cost in garbling and bandwidth. Theoretical analysis suggests that for evaluating the nine examined ciphers, one can expect a 4- to 70-fold improvement in evaluation performance with, at most, a 4-fold increase in garbling cost and, at most, an 8-fold increase in communication cost compared to the Half-Gates (Zahur, Rosulek and Evans; Eurocrypt'15) and ThreeHalves (Rosulek and Roy; Crypto'21) garbling schemes. In an offline/online setting, such as secure function evaluation as a service, the circuit garbling and communication to the evaluator can proceed in the offline phase. Thus, our scheme offers a fast online phase. Furthermore, we present efficient Boolean circuits for the S-boxes of TWINE and Midori64 ciphers. To our knowledge, our formulas give the smallest number of AND gates for the S-boxes of these two ciphers.

#### I. INTRODUCTION

Privacy-preserving protocols enable collaborative computation on sensitive data while protecting the privacy of the sensitive data. Successful implementations in a two-party scenario include privacy-preserving genome analysis [1], email spam filtering [2], image processing [3] and machine learning [4]. The formalization of such two-party computation is called Secure Function Evaluation (SFE). Here the two parties, namely, Alice and Bob, want to compute a public function f(x, y), where x is the input of Alice and y is the input of Bob, without revealing their input to each other. Yao's garbled circuit protocol [5] has become a practical solution for SFE due to improved constructions. Moreover, garbling schemes (derived from the original garbled circuit construction) have also been identified as a useful cryptographic primitive. Most of the previous works focus on projective garbling schemes that assign two values to a wire, 0 and 1, such as the garbling scheme Half-Gates by Zahur et al. [6] or the ThreeHalves scheme by Rosulek and Roy [7].

This paper considers garbling schemes in the offline/online setting. The offline phase performs function-dependent preprocessing. Concretely, the garbler garbles the circuit computing f and transmits the garbled gates to the evaluator but withholds the wire labels for the input layer. Once the input data of the garbler and the evaluator is available, the parties engage to obtain the appropriate wire labels for their respective inputs. Then, the evaluator evaluates the garbled circuit. The offline phase can be performed ahead of time and even batched to allow for optimal use of hardware and bandwidth if multiple function evaluations are expected. Hence, the online time, i.e., the time from having obtained the respective inputs to the evaluated output of the garbled circuit, is essential in this setting. This offline/online setting enables an efficient SFE as a service where the SFE service providers agree on a set of useful functions. The offline phase is run when the system is under low load and pre-processing results are stored. This way, the user of the service benefits from improved online times.

In this work, we examine a projective garbling scheme that assigns  $2^n$  values to a wire. As a consequence, each wire in the circuit carries the semantics of an *n*-bit string. We generalize the encoding of FreeXOR by Kolesnikov and Schneider [8] to obtain a scheme where bitwise-XOR between *n*-bit strings is free. Our scheme allows fast evaluation of highly non-linear functions with n input bits at a moderate additional garbling and bandwidth cost in the offline phase. We demonstrate this trade-off by implementing several symmetrickey primitives (SPN block ciphers with a cell structure as explained in Sect. VI) and describe two application scenarios in Sect. VI-C: distributed decryption in IoT-to-Cloud Secure Computation and distributing the key distribution center in the Kerberos authentication protocol. Garbling schemes for Boolean circuits need to express the non-linear S-box layer in the SPN primitives required in these two applications using multiple AND gates (e.g., for AES 32 AND gates) which translates to 64 and 96 hash function calls to evaluate each AES S-box in [6] and [7], respectively. With our garbling scheme, evaluation of the entire S-box is done with one lookup table evaluation that costs one hash function call, yielding a speed-up by a large factor.

While the new garbling scheme assumes semi-honest adversaries, i.e. neither the garbler nor the evaluator may deviate from the protocol, several general approaches exist to make a garbled circuit protocol secure in the presence of active adversaries, which are allowed to deviate arbitrarily from the protocol. Prominent examples are based on cut-and-choose [9], [10], [11], [12], on zero-knowledge proofs [13], [14] and authenticated garbling [15], [16], [17]. Moreover, semi-honest garbling schemes can be compiled into actively secure three party protocols in the honest majority setting [18].

1) Technical Overview: The core ideas of the scheme are summarized as follows. We encode an *n*-bit string with bits  $x_1, x_2, \ldots x_n$  into a wire label as

$$W \oplus x_1 R_1 \oplus x_2 R_2 \oplus \cdots \oplus x_n R_n$$

,

where W is a random label. We call  $R_i$  the wire label offsets that are randomly chosen by the garbler but fixed for all encodings in the circuit (see Definition 1 for details) and if  $x_i = 1$ ,  $x_i R_i$  is  $R_i$ , otherwise it is the zero string. For

COSIC KU Leuven, Belgium.

This work is supported by CyberSecurity Research Flanders with reference number VR20192203 and by the Flemish Government through FWO SBO project MOZAIK S003321N.

n = 1, this is the encoding of FreeXOR. Note that in previous garbling schemes with point-and-permute the wire labels have length  $\approx \kappa^1$  while our encoding requires a length of  $\kappa + n$ with  $\kappa$  the security parameter. We define two types of gates, XOR and projection gates. XOR gates compute the bitwise-XOR of two *n*-bit strings, require little garbling and evaluation work and are non-interactive, making them practically free. A projection gate computes any *n*-bit to *m*-bit function on a wire value by using Yao's garbled table lookup, i.e., encrypting output wire labels using the respective input wire label as key. We apply standard garbled row reduction [19] and point-andpermute techniques [20]. For a projection gate, the garbler's work is  $2^n$  calls to the encryption primitive, and  $2^n - 1$ ciphertexts have to be sent to the evaluator, each ciphertext has size  $\kappa + m$  bits. However, the evaluator only makes a single call to the encryption primitive, independent of the "size" n of the projection gate. This makes the scheme attractive in the pre-processed garbled circuit model since any nonlinear *n*-bit functionality can be evaluated with one call to the cryptographic primitive.

2) Contributions: We present a projective garbling scheme that assigns *n*-bit strings to each wire and in which XOR gates are free. The specific encoding of an *n*-bit string in a label allows seamless integration into existing garbling schemes that assign two values per wire. Following the spirit of modular proofs, we identify necessary properties of the cryptographic primitive (denoted by  $\mathcal{H}$ ) that is used to encrypt the truth table. Subsequently, we obtain a generalization of tweakable circular correlation robustness (TCCR, first defined by Choi et al. [21]), which we call *n*-TCCR, for  $\mathcal{H}$ .

We apply the garbling scheme to compute nine symmetrickey primitives that follow a cell-based SPN architecture which is described in Sect. VI, including AES, CRAFT, Fides, MANTIS, Midori, Piccolo, SKINNY, TWINE and WAGE. For these, we show a significant improvement in evaluation work in the online phase over the state-of-the-art schemes Half-Gates [6] and ThreeHalves [7] that is traded off with moderate additional garbling work and/or communication cost in the offline phase. Table I shows the estimated evaluation improvement based on calls to  $\mathcal{H}$ , which is complemented by a practical implementation in Sect. VI that shows that this evaluation improvement translates into practice (see Table VII). Our code is publicly available<sup>2</sup>. We obtain evaluation times for, e.g., AES as low as 0.016 ms.

Furthermore, to facilitate implementation, we give Boolean circuits for the S-boxes of TWINE [22] and Midori64 [23], which is also used in MANTIS [24] and CRAFT [25], using only AND and XOR gates. To the best of our knowledge, our Boolean circuits give the smallest number of AND gates for these two ciphers, namely, 6 AND gates for TWINE's 4-bit S-box and 4 AND gates for the Midori64 Sb<sub>0</sub> S-box. Details can be found in Appendix A.

3) Organisation: The rest of the paper is organized as follows. In Sect. II, we review related work on garbling schemes. Section III gives more details on previous work

<sup>1</sup>To be precise: In, e.g., [6], [7] the wire label length  $k = \kappa + 1$  since one bit is used as pointer bit.

Table I: Evaluation work improvement for selected symmetric primitives over Half-Gates [6]. Garbling and communication trade-off is listed in Table VI.

| Primitive       | Evaluation<br>Improvement |              | Primitive       | Evaluation<br>Improvement |              |

|-----------------|---------------------------|--------------|-----------------|---------------------------|--------------|

| Hal             | f-Gates                   | ThreeH       | Ialves          | Half-Gates                | ThreeHalves  |

| AES-128 [26]    | $26 \times$               | $39 \times$  | Piccolo-128     | $4.5 \times$              | $6.8 \times$ |

| CRAFT [25]      | $5.7 \times$              | $8.5 \times$ | SKINNY-64-64 [2 | [4] 7×                    | $10 \times$  |

| Fides-80 [27]   | $15 \times$               | $23 \times$  | SKINNY-64-128   | $4.6 \times$              | $7 \times$   |

| Fides-96        | $50 \times$               | $75 \times$  | TWINE-80 [22]   | 9.8 	imes                 | $14 \times$  |

| MANTIS [24]     | $4.3 \times$              | $6.4 \times$ | TWINE-128       | $9 \times$                | $13 \times$  |

| Midori64 [23]   | $5.3 \times$              | $8 \times$   | WAGE [28]       | $72 \times$               | $109 \times$ |

| Piccolo-80 [29] | $4.7 \times$              | $7 \times$   |                 |                           |              |

which we build upon. We present our scheme in Sect. IV and prove its security in Sect. V. A comparison of the state of the art and our scheme for nine (lightweight) symmetric primitives is given in Sect. VI. Finally, we conclude the paper in Sect. VII.

# II. RELATED WORK

Recent improvements on Yao's garbled circuit protocol in the passive security setting focus on lowering bandwidth requirements, e.g., [30], [31]. In the line of work [20], [19], [8] leading to the state-of-the-art schemes Half-Gates [6] and ThreeHalves [7], AND gates only require to send  $2\kappa$  bits and  $\approx 1.5\kappa$  bits, respectively, where  $\kappa$  is a security parameter, while XOR gates are free. Acharya et al. [32] propose an approach to garbling where the garbled gate is no longer composed of ciphertexts from individual rows in the truth table, focusing only on binary gates.

While computation with binary values is mainly expressed in Boolean circuits with binary gates, gates with more inputs than two or more outputs than one have been studied as well. Dessouky et al. [33] define those gates as lookup tables and show how they can be evaluated in the passive security case in the Goldreich-Micali-Wigderson protocol [34]. FLUTE [35] improves both setup and online cost of [33]. Damgård et al. [36], [37] design a table lookup for twoparty secure computation and Keller et al. [38] extend it to the multi-party case based on secret-sharing. The basis for the aforementioned constructions is the one-time truth-table protocol OTTT by Ishai et al. [39]. Table II compares the (estimated) communication cost of these approaches for a 4bit and 8-bit lookup table, respectively. Note that the aforementioned protocols require a function-dependent number of communication rounds in the online phase. While the local computations are faster than garbled circuit evaluation, the impact of network latency delaying the online computation time in this case is significantly increased by factor  $\approx 10 \times$  to  $40 \times$  for the SPN primitives (since they have 10 to 40 rounds). We aim to minimize online computation latency.

AES as a function has been studied explicitly by Durak and Guajardo [40], SKINNY and Photon were studied by Abidin et al. [41]. However, both works are in the arithmetic setting.

In the garbled circuit domain, Fairplay [42] and TASTY [44] already compute larger gates. Huang et al. [43] focus on an 8-bit to 8-bit AES S-box gate. Heath and Kolesnikov [46]

<sup>&</sup>lt;sup>2</sup>https://github.com/KULeuven-COSIC/gc-fast-sbox-eval

Table II: Comparison of pre-processed lookup table (LUT) approaches in MPC protocols for  $\kappa = 128$ . The depth of the circuit is denoted by *d*. Total communication is denoted in kilobytes (kB).

| Scheme                                         | Round<br>Complexity               | Total Con<br>(4-bit LUT)                      | nm. in kB<br>(8-bit LUT)                             |

|------------------------------------------------|-----------------------------------|-----------------------------------------------|------------------------------------------------------|

| OTTT [39] (from [33, Table IV])                | $\mathcal{O}(d)$                  | $\approx 6$                                   | $\approx 262$                                        |

| MiniMAC AES [37]                               | $\mathcal{O}(d)$                  | -                                             | $\approx 700$                                        |

| SP-LUT [33, Table IV]<br>OP-LUT [33, Table IV] | $\mathcal{O}(d) \ \mathcal{O}(d)$ | $\begin{array}{c} 0.039 \\ 0.159 \end{array}$ | $\begin{array}{l} 0.288 \\ \approx 65.5 \end{array}$ |

| FLUTE [35, Table 2]                            | $\mathcal{O}(d)$                  | 0.007                                         | 0.133                                                |

| Fairplay [42], Huang et el. [43]               | $\mathcal{O}(1)$                  | 1.024                                         | 32.768                                               |

| TASTY [44]                                     | $\mathcal{O}(1)$                  | 0.96                                          | 32.64                                                |

| Heath et al. [45]                              | $\mathcal{O}(1)$                  | 0.312                                         | 1.392                                                |

| This work                                      | $\mathcal{O}(1)$                  | 0.247                                         | 4.335                                                |

construct a garbling gadget that computes a one-hot outerproduct of two bit-vectors, which can be used to select one entry from a truth-table based on an index known by the evaluator. This approach has later been adapted to secret access to arbitrary truth-tables [45]. But unlike our scheme, these works consider multiple wires instead of multiple values per wire. They also do not provide any security proof for the larger gates and Fairplay is vulnerable to attacks with malformed circuits [47]. Computing a gate with multiple input wires necessitates more generic hash function constructions that operate on inputs longer than one block. Practical performance improvements are due to the use of AES-NI instructions in permutation-based constructions such as [48], [49], [50]. It is unclear how these constructions extend to the multi-input case in the context of garbled circuits. Our scheme uses a cryptographic primitive with fixed-length input, enabling the use of AES-NI instructions. An overview of garbling and evaluation work, circuit size and the hash function construction for a generic *n*-to-*m*-bit gate is given in Table III.

Lindell and Yanai [51] investigate a projective garbling scheme with wires holding three-valued logic values but conclude that a translation into Boolean circuits is more efficient.

Since the work of Ball et al. [52] is conceptually very close to ours, we discuss it in detail in Sect. III-A. The main difference is that their scheme uses arithmetic circuits in  $\mathbb{Z}_m$ , where addition modulo an integer is free, while our proposal sticks to a bit representation where XOR is free. This difference is essential for an efficient representation of SPN primitives that we target in this work. For m > 2(otherwise it degenerates to a Boolean circuit for which [6], [7] offer better performance), XOR is a non-linear operation and thus would incur communication cost. Bitwise-XOR could either be emulated as x + y - 2xy where x, y are  $\mathbb{Z}_m$ encoded bits. This costs one multiplication gate per XOR, or n multiplication gates to compute bitwise-XOR of n-bit strings, respectively. Alternatively, using projection gates in  $\mathbb{Z}_m$  computing  $\phi(x,y) = x \oplus y$  for  $x,y \in \mathbb{Z}_{2^n}$  would require  $2^{n+1} - 1$  ciphertexts to be sent (disregarding the cost to compute x||y| as input first). Since in our scheme, XOR

| Scheme                 | Primitive | Garbling Work                        | Circuit Size<br>(in bits)                             | Evaluation Work                    |

|------------------------|-----------|--------------------------------------|-------------------------------------------------------|------------------------------------|

| Fairplay [42]          | SHA-1     | $2^n\cdot m\cdot 2$                  | $2^n m \kappa$                                        | $m \cdot 2$                        |

| TASTY [44]             | SHA-256   | $2^n \cdot m$                        | $(2^n - 1)m\kappa$                                    | m                                  |

| Huang et al. [43]      | SHA-1     | $2^n\cdot \lceil \kappa m/160\rceil$ | $2^n m \kappa$                                        | $\lceil \kappa m/160 \rceil$       |

| Heath et al. [45]      | AES-NI    | $\geq 2^n(1+m/\kappa) \\ +nm$        |                                                       | $\geq 2^n (1 + m/\kappa)) \\ + nm$ |

| This work $^{\dagger}$ | AES-NI    | $2^n$                                | $\begin{array}{l}(2^n-1)\kappa\\+(2^n-1)m\end{array}$ | 1                                  |

Table IV: Notation.

| $\kappa$                                                        | Security parameter                                                      |

|-----------------------------------------------------------------|-------------------------------------------------------------------------|

| v                                                               | Bold letters denote vectors                                             |

| $\{0,1\}^{l}$                                                   | The set of bit-vectors of length $l$                                    |

| $W^{\beta}_{\alpha}$                                            | The wire label of wire $\alpha$ that encodes the value $\beta$          |

| $A \oplus B$                                                    | Bitwise XOR for $A, B \in \{0, 1\}^l$                                   |

| A  B                                                            | Bit-vector concatenation for $A \in \{0, 1\}^l$ , $B \in \{0, 1\}^{l'}$ |

| $\begin{array}{c} \{A, B\}    C \\ x' \leftarrow x \end{array}$ | Bit-vector concatenation extended to sets, i.e., $\{A     C, B     C\}$ |

| $x' \leftarrow x$                                               | Assignment of value $x$ to $x'$                                         |

| $x \leftarrow \{a, b, c, \dots\}$                               | Uniform sampling from the set $\{a, b, c,\}$                            |

is linear, no ciphertexts need to be sent. We estimate that computing, e.g., SKINNY-64-128 in  $\mathbb{Z}_m$  representation would be at least 3–4 times slower in all metrics compared to our scheme.

# III. BACKGROUND

We start with the arithmetic circuit scheme by Ball et al. [52] in Sect. III-A and detail the security model by Bellare, Hoang and Rogaway (BHR) [53] in Sect. III-B. Table IV lists the notation used throughout the paper.

## A. Garbled Circuits for Bounded Integers

Ball et al. [52] propose a scheme based on garbled circuits that assigns integers  $x \in \mathbb{Z}_m$  to each wire in the circuit. In this representation, addition (in  $\mathbb{Z}_m$ ) is free in the same sense as FreeXOR. We briefly describe their scheme as our scheme is similar but represents *n*-bit strings per wire instead of numbers in  $\mathbb{Z}_m$ .

The wire encoding of  $x \in \mathbb{Z}_m$  is  $W_i^x = W_i^0 + x \odot \Delta_m$ , where  $W_i^0, \Delta_m \in \mathbb{Z}_m^{\lambda_m}, \lambda_m = \lceil \frac{\kappa}{\log_2 m} \rceil$ . Addition is component-wise in the ring  $\mathbb{Z}_m$ . Here  $\odot$  denotes a scalar multiplication. For each  $m, \Delta_m$  is a secret, random vector known by the garbler.

The scheme mainly offers two types of gates, addition and unary projection. For addition of wires a and b with output wire c, let  $W_a^0, W_b^0$  be the two input wire labels of zero, then the garbler computes  $W_c^0 = W_a^0 + W_b^0$  as the output zero label. The evaluator, given  $W_a^x$  and  $W_b^y$  for evaluation, computes

$$W_c^{x+y} = W_a^x + W_b^y = \underbrace{W_a^0 + W_b^0}_{W_c^0} + (x+y) \odot \Delta_m .$$

Addition incurs neither transmitted ciphertexts nor invocations of the encryption primitive. Let  $\phi : \mathbb{Z}_n \to \mathbb{Z}_m$  be an arbitrary function. The projection gate  $\operatorname{Proj}_{\phi}$  computes the operation  $x \mapsto \phi(x)$ . Let G be the garbled table, then the garbler fills G[x+r] for every  $x \in \mathbb{Z}_n$  as follows:

$$H(W_a^0 + x \odot \Delta_n) + W_c^0 + \phi(x) \odot \Delta_m = H(W_a^x) + W_c^{\phi(x)}$$

where r is the secret cyclic shift offset. We can reduce the number of ciphertexts per projection gate to n-1 by applying garbled row reduction. The zero label is obtained when r = -x,  $W_c^0 = -H(W_a^{-r}) - \phi(-r) \odot \Delta_m$ , from the encryption above. This, analogous to the binary case, fixes the ciphertext of the first garbled row to  $0^{\lambda_m}$ .

Again, one element of the label can be used as a pointer and replace the shift r during garbling if  $\Delta_n$  is chosen appropriately. With this, the evaluator only has to decrypt the ciphertext the pointer indicates.

# B. Security Model by Bellare, Hoang and Rogaway

Bellare, Hoang and Rogaway [53] define a security model for garbling schemes that formalizes the principle of circuit garbling as a cryptographic primitive. Many recent garbling schemes were proven secure in their model, e.g., [6], [54], [55], [7]. As we will use the same model, we give a brief overview.

A garbling scheme is a tuple of Garble, Encode, Eval and Decode algorithms:

- Garble: Transforms the input circuit f into the tuple (GC, e, d) where GC is the garbled circuit, e is the input encoding information (e.g., all semantic labels for input wires) and d is the decoding information.

- Encode: Encodes a given input x using the semantic labels e and returns a garbled input X, e.g., the input label with semantic x.

- Eval: Evaluates the garbled circuit GC using the input wire labels {W<sub>i</sub>}<sub>i∈Inputs</sub> and returns the output wire labels {W<sub>i</sub>}<sub>i∈Outputs</sub>.

- Decode: Decodes the output wire labels  $\{W_i\}_{i \in \text{Outputs}}$ using the decoding information d and returns the plaintext output  $y \in \{0, 1\}^m$  or  $\perp$  if the output wire labels are invalid.

The garbling scheme must produce correct circuit evaluations for any circuit f and inputs  $x \in \{0,1\}^n$ . Let GC, e, d be the outputs of Garble(f), and  $X_i$  the output of  $Encode(x_i, e)$ for  $i \in Inputs$  then  $Decode(Eval(GC, \{X_i\}_{i \in Inputs}), d) = f(x)$ where f(x) denotes the circuit evaluation in the clear.

Bellare et al. define two notions of secrecy. In the privacy notion, given (GC, X, d), a party cannot learn any information besides what is revealed from the final output y and the side-information function  $\Phi$ . In our case,  $\Phi = \Phi_{topo^*}$  where only the circuit topology and the XOR gates are revealed but the function computed by projection gates remains hidden to the evaluator<sup>3</sup>. The privacy property can be achieved by giving a simulator S for the Garble function that only receives the output y and  $\Phi$ . In the code-based game in Fig. 1, the garbling scheme is prv.sim secure if for every polynomialtime adversary A there is a polynomial-time simulator S such

<sup>3</sup>In [53]  $\Phi_{topo}$  is defined as completely gate hiding, we therefore denote the slightly weaker notion with topo\*.

that Adv(prv.sim) is negligible, where

$$Adv(prv.sim) = \left| \Pr[\mathcal{A} \text{ wins } prv.sim] - \frac{1}{2} \right| = \left| \Pr[b = b'] - \frac{1}{2} \right|$$

Intuitively, if the output of the simulator is indistinguishable from the output of Garble and Encode on a circuit and input chosen by the adversary, the scheme is prv.sim secure. In the notion of obliviousness obv.sim, the adversary does not learn the decoding function. So given (GC, X), a party cannot learn any information besides the side-information  $\Phi$ . The advantage is defined analogously to Adv(prv.sim).

(a) Game prv.sim $_{\Phi,S}$ . (b) C

(b) Game obv.sim $_{\Phi,S}$ .

Figure 1: For every circuit f and input x of the adversary's choice, the respective game function is called and the adversary outputs a choice b' given (GC, X, d) (resp. (GC, X)). The adversary wins if b = b'.

#### IV. THE SCHEME

In Sect. IV-A, we first describe the notation for a circuit comprising XOR gates and projection gates. Then, we detail how the garbler encodes *n*-bit strings and transforms them into wire labels. Next, in Sect. IV-B, we show how XOR gates are garbled and evaluated, followed by a description of how projection gates are garbled and evaluated. Section IV-C describes higher-level gadgets that can be obtained from the aforementioned gates. In Sect. IV-D, all concepts are pieced together to describe the garbling, evaluation and decoding function. We also describe how input is handled. The complete garbling scheme  $\Pi$  is given in Fig. 2. We start with some general notations. Let  $lsb_n(W)$  be the *n* least significant bits<sup>4</sup> of the bit-vector  $W \in \{0,1\}^k$ . With k we denote the wire label length. We use a hash function  $\mathcal{H}: \{0,1\}^k \times \{0,1\}^{\tau} \rightarrow \{0,1\}^{\tau}$  $\{0,1\}^k$  that accepts a k-bit input, a  $\tau$ -bit tweak and outputs k bits. Further properties of  $\mathcal{H}$  are presented in Sect. V-A.

# A. Circuit Definition

We define a circuit with a *p*-bit input and *q* gates. The function computed by the circuit is denoted by *f*. Let the wire index be  $1, \ldots, p, p+1, \ldots, p+q$ , where the input wires have index  $1, \ldots, p$  and the output wire of the *i*-th gate has index p+i. We denote the set of input wire indices as Inputs, and the set of output wire indices as Outputs. We associate a bit-length  $\ell(i)$  to each wire *i*. Let  $\bar{n}$  denote the maximum bit-length of wires used in *f*, then we use bit strings of length  $k = \kappa + \bar{n}$  as wire labels. Let Gates be a topologically sorted list of gates  $G_1, \ldots, G_q$ . We distinguish two types of gates:

<sup>&</sup>lt;sup>4</sup>The exact location of the n bits in W is not important for the scheme as long as it is consistently used by both parties.

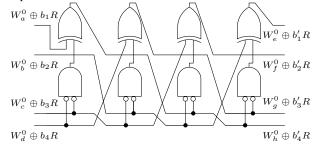

Parameters:  $\bar{n}$  maximum bit-length of wires in f, k wire label length with  $k = \kappa + \bar{n}$ 1: function  $\text{GENR}(\bar{n})$ 2: for  $i \in \{1, ..., \bar{n}\}$  do ⊳ cf. Definition 1 3:  $\mathbf{R}_i \leftarrow \mathcal{R}_i$ return  $\mathbf{R}_1, \ldots, \mathbf{R}_{\bar{n}}$ 4: 5: **function** GARBLE(f) $\mathbf{R}_{1}, \dots, \mathbf{R}_{\bar{n}} \leftarrow \operatorname{GENR}(\bar{n})$ for  $i \in \operatorname{Inputs} \operatorname{\mathbf{do}}$  $W_{i}^{0^{\ell(i)}} \leftarrow \{0, 1\}^{k}$ 6: 7: 8: for  $G_i \in Gates do$ 9.  $\begin{array}{l} \text{if } \mathbf{G}_i = XOR \text{ then} \\ W_i^{0^n} \leftarrow W_a^{0^n} \oplus W_b^{0^n} \end{array}$  $\triangleright$  G<sub>i</sub> with *n*-bit input wires *a*,*b* 10: 11: 12: else  $\triangleright G_i$  with *n*-bit input wire *a*  $W_i^{0^m} \leftarrow \$ \{0, 1\}^k$ for  $x \in \{0, 1\}^n$  do  $\triangleright$  and  $\phi: \{0,1\}^n \rightarrow \{0,1\}^m$ 13: 14:  $\begin{array}{l} \operatorname{Kor} u \in \{0, 1\} \quad \text{uo} \\ GC[i, \operatorname{lsb}_n(W_a^x)] \leftarrow \mathcal{H}(W_a^x, i) \oplus W_i^{0^m} \oplus \phi(x) \cdot \mathbf{R}_m \\ d \leftarrow \{\operatorname{lsb}_{\ell(i)}(W_i^{0^{\ell(i)}})\}_{i \in \operatorname{Outputs}} \\ e \leftarrow \{W_i^{0^{\ell(i)}}\}_{i \in \operatorname{Inputs}}, \mathbf{R}_1, \dots, \mathbf{R}_{\bar{n}} \\ \operatorname{return} GC, e, d \end{array}$ 15: 16: 17: 18: 19: function  $ENCODE(e, \{x_i\}_{i \in Inputs})$ for  $i \in$  Inputs do 20:  $X_i \leftarrow W_i^{0^{\ell(i)}} \oplus x_i \cdot \mathbf{R}_{\ell(i)}$ 21: **return**  $\{X_i\}_{i \in \text{Inputs}}$ 22: 23: function EVAL(GC,  $\{W_i\}_{i \in \text{Inputs}}$ ) for  $G_i \in Gates$  do 24. 25: if  $G_i = XOR$  then  $\triangleright G_i$  with input wires a, b  $W_i \leftarrow W_a \oplus W_b$ 26:  $\triangleright G_i$  with *n*-bit input wire *a* 27: else  $W_i \leftarrow \mathcal{H}(W_a, i) \oplus GC[i, \mathrm{lsb}_n(W_a)]$ 28: return  $\{W_i\}_{i \in \text{Outputs}}$ 29: 30: function DECODE( $\{W_i\}_{i \in \text{Outputs}}$ ) for  $i \in \text{Outputs do}$ 31:  $y_i \leftarrow d_i \oplus \mathrm{lsb}_{\ell(i)}(W_i)$ 32: 33: return y

Figure 2: The new garbling scheme  $\Pi$  comprises a garble, evaluation, encoding and decoding function.

XOR and projection gates. XOR gates accept two wires of the same bit-length n as input and output a wire with bit-length n. The unary projection gate accepts one n-bit wire and outputs one m-bit wire.

**Definition 1** (Wire Label Offsets). For each bit-length n  $(1 \le n \le \overline{n})$  that is used in f, a wire label offset is a bit-vector of length  $k = \kappa + n$  with  $\kappa$  random bits and n fixed bits. The garbler draws the matrix  $\mathbf{M}$  uniformly at random from  $\{0,1\}^{\kappa \times n}$  and appends fixed bits to each column-vector to form  $\mathbf{R}_n = \begin{pmatrix} \mathbf{M} \\ \mathbf{I}_n \end{pmatrix}$ , where  $\mathbf{I}_n \in \{0,1\}^{n \times n}$  is the identity matrix. The column vector  $R_i$  in  $\mathbf{R}_n$  is the *i*-th wire label offset. We denote the distribution from which  $\mathbf{R}_n$  is sampled  $\mathcal{R}_n$ , i.e.,  $\mathbf{R}_n \leftarrow \mathcal{R}_n$ .

The matrix  $\mathbf{R}_n$  is used throughout the whole circuit for all wires of bit-length n. We use the last n bits of the label to fix distinct values to allow point-and-permute [20]. The inner product of  $x \cdot \mathbf{R}_n$  is defined as  $x_1 R_1 \oplus \ldots \oplus x_n R_n$ .

**Definition 2** (Wire Label Encoding). The encoding  $W_i^x$  of an *n*-bit string  $x \in \{0, 1\}^n$  on a wire with index *i* is defined as  $W_i^x = W_i^{0^n} \oplus x \cdot \mathbf{R}_n$ .

Note, this yields a unique encoding for all x and  $\mathbf{R}$  even if the random part  $\mathbf{M}$  is linearly dependent in the columns because the lower n bits of  $x \cdot \mathbf{R}$  are always unique due to  $\mathbf{I}_n$ .

Intuitively, there are n distinct offsets R, one for each encoded bit. The offset applied to a wire label that encodes x is the linear combination of R values.

# B. Gates

For an XOR gate with *n*-bit input wires *a* and *b*, and output wire *c*, the garbler generates the output wire label  $W_c^x \leftarrow W_a^{0^n} \oplus W_b^{0^n} \oplus x \cdot \mathbf{R}_n$  where  $x \in \{0,1\}^n$ . No ciphertext is sent.

To evaluate an XOR gate, let  $W_a$  and  $W_b$  be the wire labels that the evaluator obtained as input labels for the XOR gate. The output label is then computed as  $W_c \leftarrow W_a \oplus W_b$ .

A projection gate  $\operatorname{Proj}_{\phi}$  computes the unary projection  $\phi: \{0,1\}^n \to \{0,1\}^m$ , a *n*-to-*m*-bit function. Let *a* be the input wire index to the projection gate and *c* be the index of the output wire, the garbler first draws the output wire label for 0 at random:  $W_c^{0^m} \leftarrow \{0,1\}^k$  and then generates  $2^n$  ciphertexts for each  $x \in \{0,1\}^n$  and stores the result in the garbled table at the position indicated by the pointer bits, i.e.,  $GC[c, \operatorname{lsb}_n(W_a^x)] \leftarrow \mathcal{H}(W_a^x, c) \oplus W_c^{\phi(x)}$ . We apply the row-reduction technique [19] and reduce the number of ciphertexts that need to be sent by one. Let *a* be the input wire index to the projection gate  $\operatorname{Proj}_{\phi}$  and *c* be the index of the output wire. Then, the garbler chooses the output wire label for  $0^m$  as

$$W_c^{0^m} = \mathcal{H}(W_a^{\mathrm{lsb}_n(W_a^{0^n})}, c) \oplus \phi(\mathrm{lsb}_n(W_a^{0^n})) \cdot \mathbf{R}_m$$

and computes the remaining ciphertexts as described above. Since the first ciphertext (where  $x = lsb_n(W_a^{0^n})$ ) is always  $0^k$ , it does not need to be sent. The number of rows sent to the evaluator is therefore  $2^n - 1$ .

For evaluation, let  $W_a$  be the wire label that the evaluator obtained as input to the projection gate. The output label  $W_c$ is computed by

$$W_c \leftarrow GC[c, \mathsf{lsb}_n(W_a)] \oplus \mathcal{H}(W_a, c)$$

,

where the position of the ciphertext to evaluate is indicated by the pointer bits of the input wire label. The first ciphertext is set to 0:  $GC[c, 0^n] = 0^m$ .

### C. Circuit Constructions

Below, we give useful gadgets comprised of XOR and projection gates.

Wire Composition. We can compose an *n*-bit wire *a* with an *m*-bit wire *b* resulting in a (n + m)-bit wire *c*. The composition construction computes the functionality  $\begin{array}{l} f: \{0,1\}^n \times \{0,1\}^m \to \{0,1\}^{n+m} \mbox{ defined by } f(x,y) = x ||y. \mbox{ The composition is then } W_c \ \leftarrow \mbox{ Proj}_s(W_a) \oplus \mbox{ Proj}_{s'}(W_b), \mbox{ where } s: \{0,1\}^n \to \{0,1\}^{n+m} \mbox{ is defined as } s(x) = x ||0^m \mbox{ and } s': \{0,1\}^m \to \{0,1\}^{n+m} \mbox{ is given as } s'(y) = 0^n ||y. \mbox{ Wire composition costs } 2^n + 2^m \mbox{ ciphertexts to garble and two ciphertexts to evaluate.} \end{array}$

Note that the construction is not limited to two arguments. It is efficient to compose many wires together at once instead of cascading or using a tree-based approach<sup>5</sup>. E.g., to compose four 1-bit wires a, b, c, d, we may use

$$\operatorname{Proj}_{s_{-}}(W_{a}) \oplus \operatorname{Proj}_{s_{+}}(W_{b}) \oplus \operatorname{Proj}_{s_{-}}(W_{c}) \oplus \operatorname{Proj}_{s_{-}}(W_{d})$$

where  $s_a(x) = 000||x, s_b(x) = 00||x||0, s_c(x) = 0||x||00, s_d = x||000$ . This costs  $4 \cdot 2^1 = 8$  ciphertexts (or 4 with row reduction) instead of  $4 \cdot 2^1 + 2 \cdot 2^2 = 16$  (resp. 10) ciphertexts.

- Wire Decomposition. Likewise, we can decompose, i.e., split, a 2*n*-bit wire into two *n*-bit wires. Let  $W_a$ be a 2*n*-bit wire, then the decomposition construction computes  $f : \{0,1\}^{2n} \rightarrow \{0,1\}^n$  defined as  $f(x_1||\ldots||x_{2n}) = x_1||\ldots||x_n$  and  $f' : \{0,1\}^{2n} \rightarrow \{0,1\}^n$  as  $f'(x_1||\ldots||x_{2n}) = x_{n+1}||\ldots||x_{2n}$  via two projection gates. Note that this time, a tree-like decomposition, e.g., from 4-bit to 2-bit to 1-bit, is more efficient than constructing four projections from 4-bit to 1-bit. The latter costs  $4 \cdot 2^4 = 64$  ciphertexts (60 with row reduction) while the former costs  $2 \cdot 2^4 + 4 \cdot 2^2 = 48$  (resp. 42) ciphertexts.

- **Constants.** In the garbling scheme, we can encode public constants or constants known only to the garbler at no cost. Let  $x \in \{0,1\}^n$  be the constant for the *n*-bit wire *a*, then the garbler chooses  $W_a^{0^n} \leftarrow x \cdot \mathbf{R}_n$ . This fixes the label  $W_a^x$  to  $0^k$ . No ciphertext is sent to the evaluator. Likewise, the evaluator uses  $W_a = 0^k$  for further evaluation.

# D. Garbling Scheme

We now describe the complete garbling scheme (see Fig. 2).

- **Garble.** The garbler chooses  $\bar{n}$  matrices of offset values (see Definition 1). For each input bit *i*, a wire label  $W_i^0$  is chosen uniformly at random. The garbling process applies the operations for projection and XOR gates as described in Sect. IV-B gate-by-gate in topological order. In the end, the garbling routine outputs the ciphertexts, input wire values, offsets and decoding information.

- Encoding and Oblivious Transfer. The garbler encodes their own input by picking the respective wire label. In Yao's protocol, the evaluator obtains the appropriate wire labels that correspond to its input via oblivious transfer (OT) [56]. Using OT extensions [39], [57] speeds this up in practice. To obtain the correct label for an *n*-bit wire, one could simply perform a 1-out-of- $2^n$  OT. Naor and Pinkas [58] show how to reduce this to *n* 1-out-of-2 OTs by introducing additional pseudorandom function (PRF) evaluations. However, using the FreeXOR property of

our scheme, we can instead perform only n 1-out-of-2 OTs (as in a garbling scheme with 2 wire labels). For each input bit  $b_i$  at position i, the sender sends

$$\begin{array}{ll} W_i^{0^n} & \text{if } b_i = 0 \,, \\ W_i^{0^n} & \oplus R_i & \text{if } b_i = 1 \,, \end{array}$$

where  $R_i$  is the *i*-th column vector in  $\mathbf{R}_n$ . To obtain the wire label for the *n*-bit wire, we XOR the obtained labels together at no additional cost. Note that  $W_i^{0^n}$  is a fresh random wire label for each bit *i* of the input.

**Evaluation and Decoding.** Once the evaluator obtains the garbled inputs, it computes the garbled output of each gate accordingly (see Sect. IV-B). Having computed the garbled output, the evaluator may either share the wire labels with the garbler or directly use the decoding information  $d_i = \text{lsb}_n(W_i^{0^n})$  for output wire  $i \in \text{Outputs}$  in the decoding function to obtain the output bits in the clear. Let us briefly look at why this decoding scheme is correct. Let i be an output wire. Since we fixed  $\text{lsb}_n(y \cdot \mathbf{R}_n) = y \cdot \mathbf{I}_n = y$  by construction of the offset values, for any value  $y \in \{0, 1\}^n$ , we have  $\text{lsb}_n(W_i^y) = \text{lsb}_n(W_i^{0^n}) \oplus y$ . As  $d_i = \text{lsb}_n(W_i^{0^n})$ , the decoding is correct

$$d_i \oplus \mathrm{lsb}_n(W_i^x) = \mathrm{lsb}_n(W_i^{0^n}) \oplus \mathrm{lsb}_n(W_i^{0^n}) \oplus \mathrm{lsb}_n(y \cdot \mathbf{R}_n) = y$$

.

# V. SECURITY

Using the BHR security model (see Sect. III-B) we show that if a hash function satisfies the properties of n-TCCR security defined in Sect. V-A below, our scheme is prv.sim (Sect. V-B) and obv.sim (Sect. V-C) secure. We sketch how to achieve authenticity in Sect. V-D.

# A. (n-)TCCR Security

We revisit the tweakable circular correlation robustness (TCCR) definition by Guo et al. [49] adapted to our notation.

**Definition 3** (TCCR Security [49]). A TCCR (tweakable circular correlation robust) hash function  $\mathcal{H}$  is a function  $\{0,1\}^k \times \{0,1\}^\tau \to \{0,1\}^k$  that accepts a message m and a tweak t. In the TCCR security game, the distinguisher  $\mathcal{D}_{\text{TCCR}}$  is given one of the two oracles with signature  $\{0,1\}^k \times \{0,1\}^\tau \times \{0,1\} \to \{0,1\}^k$

- (Real)  $\mathcal{O}_R(m,t,b) = \mathcal{H}(m \oplus R,t) \oplus bR$

- (Ideal)  $\operatorname{Rand}(m, t, b)$  is a random function.

with the goal to decide which is the oracle given to it. The distinguisher doesn't know the secret value  $R \in \{0, 1\}^k$ ,  $R \leftarrow \Re_{\text{TCCR}}$  and is only allowed to make legal queries. An illegal query is (m, t, 1 - b) if (m, t, b) has been queried before. We define the advantage as

$$\begin{aligned} \mathsf{Adv}_{\mathcal{R}_{\mathsf{TCCR}}}(\mathcal{D}_{\mathsf{TCCR}}) \\ &= \left| \Pr[\mathcal{D}_{\mathsf{TCCR}}^{\mathsf{Rand}}(1^{\kappa}) = 0] - \Pr_{R \leftarrow \mathcal{R}_{\mathsf{TCCR}}}[\mathcal{D}_{\mathsf{TCCR}}^{\mathcal{O}_{R}}(1^{\kappa}) = 0] \right| \,, \end{aligned}$$

where  $\mathcal{D}^{\mathcal{O}}$  signifies that the distinguisher has access to oracle  $\mathcal{O}$ . We call  $\mathcal{H}$  TCCR secure if  $Adv_{\mathcal{R}}(\mathcal{D}_{TCCR})$  is negligible in the security parameter  $\kappa$ .

<sup>&</sup>lt;sup>5</sup>Following the example, the tree-based approach first composes a||b and c||d resulting in 2-bit wires. Then ab||cd is composed.

Note that the advantage of  $\mathcal{D}_{\text{TCCR}}$  depends on the distribution  $\mathcal{R}_{\text{TCCR}}$  of the secret value R. Next, we define n-TCCR security, a generalized TCCR notion incorporating n secret offsets.

**Definition 4** (n-TCCR Security). A n-TCCR hash function  $\mathcal{H}$  is a function  $\{0,1\}^k \times \{0,1\}^{\tau} \to \{0,1\}^k$  that accepts a message m and a tweak t. In the n-TCCR security game, the distinguisher  $\mathcal{D}_{n-TCCR}$  is given one of the two oracles with signature  $\{0,1\}^k \times \{0,1\}^{\tau} \times \{0,1\}^n \times \{0,1\}^n \to \{0,1\}^k$

- (Real)  $\mathcal{O}_{\mathbf{R}}(m, t, \mathbf{a}, \mathbf{b}) = \mathcal{H}(m \oplus \mathbf{a} \cdot \mathbf{R}, t) \oplus \mathbf{b} \cdot \mathbf{R}$

- (Ideal) Rand $(m, t, \mathbf{a}, \mathbf{b})$  is a random function

with the goal to decide which is the oracle given to it. We interpret  $\mathbf{a}, \mathbf{b} \in \{0, 1\}^n$  as binary vectors,  $\mathbf{R} = (R_1, \ldots, R_n), \mathbf{R} \in \{0, 1\}^{k \times n} \leftarrow \mathbb{R}_n$  and  $R_i \in \{0, 1\}^k, 1 \leq i \leq n$ . The expression  $\mathbf{a} \cdot \mathbf{R} = a_1 R_1 \oplus \cdots \oplus a_n R_n$  is the linear combination of offsets defined by  $\mathbf{a}$ . The distinguisher doesn't know the secret value  $\mathbf{R}$  and is only allowed to make legal queries. An illegal query is  $\mathbf{a} = 0$  or  $(m, t, \mathbf{a}, \mathbf{b}')$  if  $(m, t, \mathbf{a}, \mathbf{b})$  has been queried before for  $\mathbf{b} \neq \mathbf{b}'$ .

We define the advantage as

$$\operatorname{Adv}_{\mathcal{R}_{n}}(\mathcal{D}_{\operatorname{n-TCCR}}) = \left| \operatorname{Pr}[\mathcal{D}_{\operatorname{n-TCCR}}^{\operatorname{Rand}}(1^{\kappa}) = 0] - \operatorname{Pr}_{\operatorname{\mathbf{R}}\leftarrow\mathcal{R}_{n}}[\mathcal{D}_{\operatorname{n-TCCR}}^{\mathcal{O}_{\operatorname{\mathbf{R}}}}(1^{\kappa}) = 0] \right|$$

We call  $\mathcal{H}$  *n*-TCCR secure if  $Adv_{\mathcal{R}_n}(\mathcal{D}_{n-TCCR})$  is negligible in  $\kappa$ .

Clearly, every n-TCCR secure hash function is also TCCR secure. Since in n-TCCR, the distinguisher has more freedom regarding queries to the oracle, a statement about the inverse direction is not straightforward.

Limitations and assumptions on TCCR are realized once instantiated with a concrete construction, e.g., the one given by [49] is secure in the random permutation model with specific bounds depending on the number of queries made by the distinguisher. In garbling schemes, the number of queries roughly translates to the number of AND gates in the garbled circuit(s) that use the same offset. Since n-TCCR is a generalization of TCCR, we expect similar assumptions and limitations. We estimate an advantage of around n-bit for the distinguisher of n-TCCR compared to TCCR when using non-dedicated TCCR constructions. This means that, to attain a similar security level as TCCR, one may need to choose larger parameters for n-TCCR.

### B. Privacy

The prv.sim definition states that given the garbled circuit GC, all the labels of the garbled input X and the decoding information d, no information is revealed about the input except from what can be deduced from the output y.

**Theorem 1.** Given a  $\bar{n}$ -TCCR secure hash function  $\mathcal{H}$  and  $\bar{n} \ll \kappa$ , the garbling scheme  $\Pi$  is prv.sim secure.

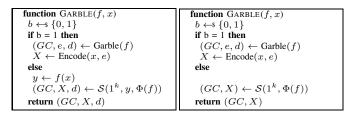

*Proof.* We define a simulator S (see Fig. 3) and show through a series of hybrids that the output of S is indistinguishable for an adversary from the output of Garble. We require  $\bar{n} \ll \kappa$ ,

1: function  $\mathcal{S}(f, y)$ for  $i \in$  Inputs do  $W_i^{0^{\ell(i)}} \leftarrow \{0, 1\}^k$ 2: 3:  $X_i \leftarrow W_i^{0^{\ell}}$ 4: for  $G_i \in Gates do$ 5: if  $\mathbf{G}_i = XOR$  then  $\mathbb{G}_i \oplus \mathbf{G}_i$  with *n*-bit input wires  $a, b = W_i^{0^n} \oplus W_b^{0^n}$ 6: 7:  $\triangleright G_i$  with *n*-bit input wire *a* and output 8: else  $\triangleright$  size *m* of the function  $G_i$  realizes  $W_i^{0^m} \leftarrow \{0,1\}^k$ 9:  $GC[i, lsb_n(W_a^{0^n})] \leftarrow \mathcal{H}_{n,m}(W_a^{0^n}, i) \oplus W_i^{0^m}$ 10: for  $x \neq 0^n \in \{0, 1\}^n$  do 11:  $GC[i, lsb_n(W_a^{0^n}) \oplus x]$ 12:  $\leftarrow \operatorname{Rand}_{n,m}(W_a^{0^n}, i, x, 0^m) \oplus W_i^{0^m}$ for  $i \in \text{Outputs } \mathbf{do}$ 13.  $d_i \leftarrow lsb_n(W_i^{0^n}) \oplus y_i$ 14: 15: return GC, X, d

i.e., the largest bit length  $\bar{n}$  used in a wire in the circuit is small compared to the security parameter  $\kappa$ , to ensure that for any adversarially chosen circuit, both the garbling scheme and the simulator run in polynomial time. In the following, we use Rand<sub>n,m</sub>(m, t, a, b) where  $\mathbf{a} \in \{0, 1\}^n$  and  $\mathbf{b} \in \{0, 1\}^m$  which can be constructed from  $\bar{n}$ -TCCR Rand by padding the a/b inputs with zeros to reach the full length of  $\bar{n}$ , e.g., Rand(m, t,  $\mathbf{a} || 0^{\bar{n}-n}$ ,  $\mathbf{b} || 0^{\bar{n}-m}$ ) since  $\bar{n} \ge n, m$  in the whole circuit. The same can be done for  $\mathcal{H}_{n,m}$  and  $\mathcal{H}$ . When evaluating a garbled circuit, let the assignment of active labels to the wires be called the active path, i.e., for input wires, the active labels are retrieved via OT, for gate outputs, the active wires are retrieved by decrypting the row denoted by the pointand-permute bits.

The idea of the simulator is to produce a garbled circuit with a fixed active path. The simulator chooses the wire labels such that

- the garbled input X that is handed to the adversary corresponds to 0<sup>p</sup>;

- the active label on each gate's output wire that the adversary obtains if they choose to evaluate the circuit with X is  $W^{0^n}$  (see Line 10 in Fig. 3).

The simulator adapts the decoding information s.t. if the garbled output is  $W^{0^n}$ , the expected output y is decoded.

$S \approx \mathcal{G}_1$ . Hybrid  $\mathcal{G}_1$  (see Fig. 4) describes the simulator from the perspective of the evaluator. Let x be the input that the adversary chooses in the game. We view x as a black box as it is unknown. Suppose we evaluated the circuit on x in plaintext. We denote  $v_i$  as the active value on wire i. Instead of fixing the active path on labels  $W^{0^n}$ , we fix it on  $W^{v_i}$ .

The output values GC, d and the outputs of S are identically distributed as  $W^{0^n}$  and  $W^{v_i}$  are both distributed uniformly at random. Further, the change of input

1: **function** EVALWIRES(f, x)for  $i \in$  Inputs do 2: 3:  $v_i \leftarrow x_i$ 4: for  $G_i \in Gates do$ 5:  $a, b \leftarrow in(\mathbf{G}_i)$ if  $G_i = XOR$  then  $\triangleright G_i$  with *n*-bit input wires *a*, *b* 6: 7.  $v_i \leftarrow v_a \oplus v_b$ 8: else  $\triangleright G_i$  with *n*-bit input wire *a*  $v_i \leftarrow \phi(v_a)$  $\triangleright$  and  $\phi: \{0,1\}^n \to \{0,1\}^m$ 9: 10: return v 11: function  $\mathcal{G}_1(f, x)$  $v \leftarrow \mathsf{EvalWires}(f, x)$ 12: 13: for  $i \in$  Inputs do  $W_{:}^{\fbox{v_i}} \leftarrow \underline{\$ \{0,1\}}^k$ 14:  $v_i$ 15: for  $G_i \in Gates$  do 16: if  $G_{\underline{i}} = XOR \underline{then}$  $\triangleright \underline{G}_i$  with *n*-bit input wires *a*, *b* 17:  $W^{v_i}$  $\leftarrow W_a^{v_a} \oplus W_b^{v_b}$ 18:  $\triangleright G_i$  with *n*-bit input wire *a* 19:  $W^{v_i}$  $\leftarrow \{0,1\}^k$ 20:  $\triangleright$  and  $\phi : \{0, 1\}^n$  $\{0,1\}^m$  $\begin{array}{c} GC[i, \mathrm{lsb}_n(W_a^{\bigsqcup l})] \leftarrow \mathcal{H}_{n,m}(W_a^{\bigsqcup l}) \\ \text{for } x \neq \boxed{v_a} \in \{0, 1\}^n \ \mathbf{do} \end{array}$ 21: 22:  $GC[i, lsb_n(W_a^{v_a}) \oplus x] \leftarrow$ 23:  $\operatorname{Rand}_{n,m}(W_a^{v_a})$  $v_a \oplus x$  $\phi(v_a \oplus x)$ for  $i \in \text{Outputs } \mathbf{do}$ 24:  $d_i \leftarrow \mathsf{lsb}_n(W_i^{\underbrace{v_i}}) \oplus y_i$ 25: return GC, X, a26:

Figure 4: Hybrid  $\mathcal{G}_1$ . The simulator from the perspective of the evaluator where x is a black box value. Values in a box  $v_i$  highlight the difference between S and  $\mathcal{G}_1$ .

arguments,

$$\begin{split} \operatorname{Rand}_{n,m}(W_a^{0^n}, i, x, 0^m) \\ &\approx \operatorname{Rand}_{n,m}(W_a^{v_a}, i, v_a \oplus x, \phi(v_a \oplus x)) \end{split}$$

does not change the distribution since all inputs  $(x, 0^m), \forall x \in \{0, 1\}^n \neq 0^n$  and  $(v_a \oplus x, \phi(v_a \oplus x)), \forall x \in \{0, 1\}^n \neq v_a$ , respectively, are unique and therefore amount to fresh randomness from the oracle, irrespective of  $\phi$ .

$\mathcal{G}_1 \approx \mathcal{G}_2$ . In hybrid  $\mathcal{G}_2$ , we replace  $\operatorname{Rand}_{n,m}$  by the real construction  $\mathcal{H}_{n,m}(m \oplus \mathbf{a} \cdot \mathbf{R}_n, t) \oplus \mathbf{b} \cdot \mathbf{R}_m$ . This change is indistinguishable for the adversary by the definition of the  $\bar{n}$ -TCCR secure function  $\mathcal{H}$  (see Definition 4)

$$\begin{aligned} & \operatorname{Rand}_{n,m}(W_a^{v_a}, i, v_a \oplus x, \phi(v_a \oplus x)) \\ & \approx \mathcal{H}_{n,m}(W_a^{v_a} \oplus (v_a \oplus x) \cdot \mathbf{R}_n, i) \oplus \phi(v_a \oplus x) \cdot \mathbf{R}_m \,. \end{aligned}$$

$\mathcal{G}_2 \approx \mathcal{G}_3$ . In hybrid  $\mathcal{G}_3$  (see Fig. 5), we no longer compute the wire values  $v_i$  explicitly from the black-box input x. We fix an encoding for  $v_i$ , namely  $v_i = 0^n$ .

For the input wires, note that  $x_i = v_i$  by definition of

EVALWIRES, so  $X_i \leftarrow W_i^{x_i}$  instead of  $W_i^{v_i}$ . Further, the ciphertext indexing  $GC[i, \cdot]$  (Line 14 in Fig. 5) is identical after the re-write. In  $\mathcal{G}_2$ ,

$$\operatorname{lsb}_n(W_a^{v_a}) \oplus x = \operatorname{lsb}_n(W_a^{0^n}) \oplus x$$

,

and in  $\mathcal{G}_3$ ,

$$\mathsf{lsb}_n(W_a^x) = \mathsf{lsb}_n(W_a^{0^n}) \oplus \mathsf{lsb}_n(x \cdot \mathbf{R}_n) = \mathsf{lsb}_n(W_a^{0^n}) \oplus x$$

by definition of  $\mathbf{R}_n$ . In the output of all gates  $G_i$ , we now maintain the invariant with  $x \in \{0,1\}^n$

$$\begin{split} & W_i^{v_i} \text{ becomes } W_i^{0^n},\\ & W_i^{v_i} \oplus (v_i \oplus x) \cdot \mathbf{R}_{\ell(i)} \text{ becomes } W_i^{0^n} \oplus x \cdot \mathbf{R}_{\ell(i)}. \end{split}$$

And for the decoding information, first note that for  $i \in$ Outputs  $v_i = y_i$ , thus in  $\mathcal{G}_2$  (we denote  $\ell(i) = n$ ),

$$d_i \oplus \mathrm{lsb}_n(W_i^{vi}) = \mathrm{lsb}_n(W_i^{v_i}) \oplus \mathrm{lsb}_n(W_i^{v_i}) \oplus y_i = y_i\,,$$

and in  $\mathcal{G}_3$ :

$$d_i \oplus \operatorname{lsb}_n(W_i^{y_i}) = \operatorname{lsb}_n(W_i^{0^n}) \oplus \operatorname{lsb}_n(W_i^{y_i})$$

=  $\operatorname{lsb}_n(W_i^{0^n}) \oplus \operatorname{lsb}_n(W_i^{0^n}) \oplus y_i$

=  $y_i$ .

The decoding information in  $\mathcal{G}_2$  and  $\mathcal{G}_3$  yield correct results when used with their respective garbled inputs.  $d_{\mathcal{G}_2}$  and  $d_{\mathcal{G}_3}$  are both uniformly distributed as  $lsb_{\ell(i)}(W_i^{vi})$  resp.  $lsb_{\ell(i)}(W_i^{0^{\ell(i)}})$  are distributed at random. So  $d_{\mathcal{G}_2}$  and  $d_{\mathcal{G}_3}$  remain indistinguishable.

We conclude the proof by noting that  $\mathcal{G}_3$  and Garble yield *identical* outputs in the prv.sim game. This can easily be seen when the exceptional case for  $x = 0^n$  (Line 21 in Fig. 5) in the projection gates part is incorporated into the loop and the computation of d is re-written,  $\mathcal{G}_3$  is a description of the Garble function.

## C. Obliviousness

The notion of obv.sim expresses that the adversary cannot learn any information given the garbled circuit GC and all input wire labels X. Unlike the privacy notion, the adversary does not have access to the decoding information d.

**Theorem 2.** Given a  $\bar{n}$ -TCCR secure hash function  $\mathcal{H}$  and  $\bar{n} \ll \kappa$ , the garbling scheme  $\Pi$  is obv.sim secure.

*Proof.* Let  $S_{\text{auth}}$  be S from Fig. 3 with the lines 13-14 removed. Then we note that the computation of GC and X doesn't depend on y, neither in  $S_{\text{auth}}$  nor in one of the hybrids  $\mathcal{G}_1, \mathcal{G}_2, \mathcal{G}_3$ . We can thus use the same reasoning as for prv.sim security, omitting parts that correspond to y or d.

## D. Authenticity

Authenticity states that an adversary cannot forge wire labels that are not obtained through evaluating the garbled circuit. Clearly, the presented scheme does not satisfy this property as any wire label is decoded to output bits. If authenticity is desired, we modify the decoding information d to list hashes of all output wire labels and associations to their semantic meaning. As in [53], the decoding function checks if the presented wire is indeed in the list d.

1: function

$$\mathcal{G}_{3}(f, x)$$

2:  $\mathbf{R}_{1}, \dots, \mathbf{R}_{\overline{n}} \leftarrow GenR(\overline{n})$

3: for  $i \in \text{Inputs do}$

4:  $W_{i}^{\bigcup 0^{\ell(i)}} \leftarrow \$ \{0, 1\}^{k}$

5:  $X_{i} \leftarrow W_{i}^{\bigcup x_{i}}$

6: for  $\mathbf{G}_{i} \in \text{Gates do}$

7:  $a, b \leftarrow in(\mathbf{G}_{i})$

8: if  $\mathbf{G}_{i} = XOR$  then  $\triangleright \mathbf{G}_{i}$  with *n*-bit input wires  $a, b$

9:  $W_{i}^{\bigcup n} \leftarrow W_{a}^{\bigcup n} \oplus W_{b}^{\bigcup n}$

10: else  $\triangleright \mathbf{G}_{i}$  with *n*-bit input wire  $a \\ \triangleright \text{ and } \phi : \{0, 1\}^{n} \rightarrow \{0, 1\}^{m}$

11:  $W_{i}^{\bigcup n} \leftarrow \$ \{0, 1\}^{k}$

12:  $GC[i, 1\mathrm{sb}_{n}(W_{a}^{\bigcup n})] \leftarrow \mathcal{H}_{n,m}(W_{a}^{\bigcup n}, i) \oplus W_{i}^{\bigcup (0^{n})}$

13: for  $x \neq 0^{n} \in \{0, 1\}^{n}$  do

14:  $GC[i, 1\mathrm{sb}_{n}(W_{a}^{\boxtimes})] \leftarrow \mathcal{H}_{n,m}(W_{a}^{\bigcup n}, i) \oplus W_{i}^{\bigcup m}$

15: for  $i \in \text{Outputs do}$

16:  $d_{i} \leftarrow 1\mathrm{sb}_{n}(W_{i}^{\bigcup n})$

17: return  $GC, X, d$

Figure 5: Hybrid  $\mathcal{G}_3$ . We fix the encoding of  $W_i^{v_i}$  to  $W_i^{0^n}$ . Values in a box  $\boxed{0^n}$  highlight the difference between  $\mathcal{G}_2$  and  $\mathcal{G}_3$ .

# VI. EVALUATION OF SPN PRIMITIVES

In the following, we discuss how SPN primitives with a specific structure can be implemented with our new garbling scheme and how this improves over the state-of-the-art. Note that we don't intend to compare the performance of the primitives among each other in MPC protocols. Instead, we focus on how each primitive can be accelerated. Consequently, we will not consider other traditional or MPC-friendly primitives, e.g., [59]. We compare the state-of-the-art garbling schemes Half-Gates [6] as well as ThreeHalves [7]. Both schemes support free XOR gates and AND gates on wires holding one bit.

In SPN-based primitives, a state is updated with a round function consisting of a substitution layer, a permutation layer, a round constant and/or (round) key addition layer. SPNs are commonly used to construct block ciphers and pseudo-random permutations used, e.g., in hash functions or MAC algorithms.

We show an efficient circuit representation with projection gates for primitives that satisfy the following conditions for state and round function parts.

- State. The state is (conceptually) split into *n*-bit cells.

- Substitution Layer. The substitution layer consists of Sboxes that are applied to each cell.

- **Permutation Layer.** The permutation layer can be described by a permutation on the cells and/or by a mixing matrix which encodes a fixed matrix multiplication with the state. In this paper, we focus on primitives with a

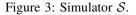

$$\underbrace{W_a^0 \oplus b_1 R_1 \oplus \cdots \oplus b_3 R_3}_{\text{Proj}_{\phi}} \underbrace{W_b^0 \oplus b_1' R_1 \oplus \cdots \oplus b_3' R_3}_{\text{Proj}_{\phi}}$$

(a) Implementation of the SKINNY 4-bit S-box via a 4-to-4-bit projection gate in our garbling scheme. Note that  $\phi$  is the S-box lookup function.

(b) Implementation of the SKINNY 4-bit S-box via Boolean circuit with input wires a, b, c, d and output wires  $e, f, g, h. b_1, \ldots, b_4$  denote the 4 input bits from least to most significant bit.  $b'_1, \ldots, b'_4$  denote the 4 output bits in the same order. Circuit from [24].

Figure 6: Example to illustrate the implementation difference between our scheme and a Boolean circuit for the 4-bit SKINNY S-box. Note that Fig. 6a encodes 4 bits *per* wire while Fig. 6b uses 4 wires.

binary mixing matrix.

• Round Constant/(Round) Key Addition Layer. The round constant or (round) key is XORed cell-wise.

With this structure, we set  $\bar{n} = n$  and implement a single cell as *n*-bit wire. Each S-box in the substitution layer is replaced with an *n*-bit projection gate computing the same functionality. The permutation layer and the addition layer are expressible with XOR gates only. We illustrate how the SKINNY 4-bit S-box is expressed in our scheme and as a Boolean circuit in Fig. 6 as an example.

We identified nine SPN primitives in the literature that fulfill the conditions. Since the studied primitives have at most 8-bit cells, we set  $\bar{n} = 8$ . These primitives include the widely-used AES standard and several established secondround and finalists of the NIST Lightweight Cryptography Competition, each offering unique hardware, performance, and energy efficiency metrics for specific real-world use cases.

#### A. Implementation Details

For the projection gates implementation, we assume that the input block is already setup in n-bit wires where n denotes the cell size in bits. This doesn't incur additional cost since the input phase using OT can already share wire labels with the desired wire label offset, as detailed in Sect. IV-D. For the implementation using AND gates, only the S-box costs AND gates in the data path of the primitive. We selected implementations for the S-boxes with the lowest number of AND gates since their cost dominates in Half-Gates and ThreeHalves. Table V details the number of projection and AND gates for each primitive.

For the 4-bit S-box used in TWINE-80 and TWINE-128 and for the 4-bit S-box used in Midori64, MANTIS and CRAFT, we found new circuits using the smallest number of AND gates so far, reducing the number of AND gates for the TWINE Sbox from 7 to 6 and for the Midori64 S-box from 8 to 4. We used the heuristic optimization tool LIGHTER by Jean et al. [60] operating on a customized cost metric, for more details see Appendix A.

For the key, we assume individual key bits to be available in 1-bit wires as this eases key scheduling in many cases. Note that the cost to transform the (round) key bits into *n*-bit wires is taken into account. In scenarios where one party knows the complete key, e.g., to offer blind symmetric encryption or decryption where the encryption or decryption is performed without learning the message and ciphertext, the key schedule does not need to be computed within the garbling scheme. Instead, if the garbler knows the key, they can compute the key schedule separately and insert the round keys as secret constants. Similarly, if the evaluator knows the key, they may receive the wire labels for round keys via OT instead.

If the key is shared among the players using a linear secretsharing scheme, for instance as  $k = k_G \oplus k_E$  where  $k_G$  is the garbler's share and  $k_E$  is the evaluator's share, the key schedule can be computed outside of the garbling scheme by each player on their share instead for ciphers with a linear key schedule, e.g., for Piccolo, Midori, SKINNY, MANTIS and CRAFT. The resulting round key shares can then be treated as input and are recombined using only linear operations saving any gates specified in the key schedule column for the cipher. However, the gate counts presented here compute the entire key schedule of the primitive which is required in the distributed encryption/decryption scenario.

# B. Performance

1) Instantiating  $\mathcal{H}$ : Before comparing our garbling scheme with Half-Gates and ThreeHalves, we need to discuss the instantiation of the *n*-TCCR hash function  $\mathcal{H}$ . Half-Gates uses a construction called TCCR for naturally derived keys, while ThreeHalves uses a randomized TCCR function. Despite minor differences, both constructions use one call to an ideal permutation (which is instantiated using fixed-key AES), which is the main computation cost. In the following comparison, we also assume that  $\mathcal{H}$  can be instantiated in a construction using only one ideal permutation call. For the practical benchmark, we use the same construction as Half-Gates. However, we need to stress a major difference: Since our wire labels are  $\kappa + n$  bits long and we still want to fit them into one permutation call, the security of our scheme is reduced by n bits with this instantiation. Concretely, since all studied primitives have  $\bar{n} \leq 8$ , Half-Gates and ThreeHalves have  $\kappa = 127$  while our scheme has  $\kappa = 120$  for AES with 128-bit block size. Should a larger security level be desired, it is also possible to encrypt the pointer bits separately with another permutation call using a dedicated construction of  $\mathcal{H}$ that has an output length of  $\kappa + n$ . We leave such construction and the required dedicated security analysis to future work.

2) Evaluation Performance: The gate counts from Table V can be turned into calls to  $\mathcal{H}$  and sent ciphertexts. In Half-Gates, each AND gate costs 4 calls to  $\mathcal{H}$  for garbling, 2 ciphertexts are sent, and 2 calls to  $\mathcal{H}$  for evaluation. In

Table V: Detailed gate counts for setup, key schedule and data path of the selected symmetric primitives. The top entry denotes the number of AND gates while the bottom entry denotes the number of projection gates.

† Gate counts obtained from Mandal et al. [61].

| Primitive       | Setup     | Key Schedule                     | Data Path                           |

|-----------------|-----------|----------------------------------|-------------------------------------|

| AES-128 [26]    |           | 1280 AND<br>128 1-bit + 49 8-bit | 5120 AND<br>320 8-bit               |

| CRAFT [25]      |           | 192 1-bit                        | 1920 AND<br>480 4-bit               |

| Fides-80 [27]   | 160 1-bit |                                  | 320 AND<br>32 5-bit                 |

| Fides-96        | 192 1-bit |                                  | 1088 AND<br>32 6-bit                |

| MANTIS [24]     |           | 192 1-bit                        | 896 AND<br>224 4-bit                |

| Midori64 [23]   |           | 128 1-bit                        | 1024 AND<br>256 4-bit               |

| Piccolo-80 [29] |           | 80 1-bit                         | 1600 AND<br>600 4-bit               |

| Piccolo-128     |           | 128 1-bit                        | 1984 AND<br>744 4-bit               |

| SKINNY-64-128   |           | 128 1-bit + 280 4-bit            | 2304 AND<br>576 4-bit               |

| TWINE-80 [22]   |           | 432 AND<br>80 1-bit + 70 4-bit   | 1728 AND<br>288 4-bit               |

| TWINE-128       |           | 630 AND<br>128 1-bit + 104 4-bit | 1728 AND<br>288 4-bit               |

| WAGE [28]       | 259 1-bit |                                  | 37745 AND <sup>†</sup><br>777 7-bit |

Table VI: Estimated performance difference for selected symmetric ciphers. The notation  $\times x$  denotes an improvement by factor x in the category with respect to the base scheme, i.e., x > 1 is an improvement, x < 1 is degradation.

| Base Scheme                       | Primitive       | Garble                                                    | Send                                                      | Eval                                                    |

|-----------------------------------|-----------------|-----------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------|

| Half-Gates [6]<br>ThreeHalves [7] | AES-128 [26]    | $\substack{\times 0.28 \\ \times 0.42}$                   | $\substack{\times 0.14 \\ \times 0.10}$                   | $\substack{\times 26.23 \\ \times 39.34}$               |

| Half-Gates<br>ThreeHalves         | CRAFT [25]      | $\substack{\times 0.95 \\ \times 1.43}$                   | $\substack{\times 0.52 \\ \times 0.39}$                   | $^{\times 5.71}_{\times 8.57}$                          |

| Half-Gates<br>ThreeHalves         | Fides-80 [27]   | $\substack{\times 1.23 \\ \times 1.84}$                   | $\substack{\times 0.64 \\ \times 0.48}$                   | $\substack{\times 15.45 \\ \times 23.18}$               |

| Half-Gates<br>ThreeHalves         | Fides-96        | $^{\times 2.10}_{\times 3.15}$                            | $\substack{\times 1.07 \\ \times 0.81}$                   | $\times 50.26 \\ \times 75.39$                          |

| Half-Gates<br>ThreeHalves         | MANTIS [24]     | $\begin{array}{c} \times 0.90 \\ \times 1.35 \end{array}$ | $\substack{\times 0.50 \\ \times 0.38}$                   | $\substack{\times 4.31 \\ \times 6.46}$                 |

| Half-Gates<br>ThreeHalves         | Midori64 [23]   | $\substack{\times 0.94 \\ \times 1.41}$                   | $\substack{\times 0.52 \\ \times 0.39}$                   | $\begin{array}{c} 	imes 5.33 \\ 	imes 8.00 \end{array}$ |

| Half-Gates<br>ThreeHalves         | Piccolo-80 [29] | $\substack{\times 0.66 \\ \times 0.98}$                   | $\substack{\times 0.35 \\ \times 0.26}$                   | $\substack{\times 4.71 \\ \times 7.06}$                 |

| Half-Gates<br>ThreeHalves         | Piccolo-128     | $\substack{\times 0.65 \\ \times 0.98}$                   | $\substack{\times 0.35 \\ \times 0.26}$                   | $\substack{\times 4.55 \\ \times 6.83}$                 |

| Half-Gates<br>ThreeHalves         | SKINNY-64-128   | $\substack{\times 0.66 \\ \times 0.99}$                   | $\substack{\times 0.36 \\ \times 0.27}$                   | $\substack{\times 4.68 \\ \times 7.02}$                 |

| Half-Gates<br>ThreeHalves         | TWINE-80 [22]   | $\substack{\times 1.46 \\ \times 2.19}$                   | $\substack{\times 0.79 \\ \times 0.59}$                   | $\substack{\times 9.81 \\ \times 14.71}$                |

| Half-Gates<br>ThreeHalves         | TWINE-128       | $\substack{\times 1.44 \\ \times 2.16}$                   | $\begin{array}{c} 	imes 0.78 \\ 	imes 0.59 \end{array}$   | $\substack{\times 9.05 \\ \times 13.58}$                |

| Half-Gates<br>ThreeHalves         | WAGE [28]       | $\times 1.51 \times 2.27$                                 | $\begin{array}{c} \times 0.76 \\ \times 0.57 \end{array}$ | $\times 72.87 \times 109.30$                            |

Table VII: Performance benchmark results for some SPNciphers comparing garbling and evaluation time as well as the circuit size. All reported numbers are amortized from 500 (for SKINNY-128-\*) and 1000 parallel primitive calls averaged over 10 repetitions.

| Base Scheme     | Primitive                | Garble<br>in ms | Circuit size<br>in KB | Eval<br>in ms |

|-----------------|--------------------------|-----------------|-----------------------|---------------|

| Half-Gates [6]  | AES-128 [26]             | 0.767           | 204.93                | 0.722         |

| ThreeHalves [7] |                          | <b>0.436</b>    | <b>156.51</b>         | 0.305         |

| This work       |                          | 0.928           | 1242.55               | <b>0.016</b>  |

| Half-Gates      | MANTIS <sub>7</sub> [24] | 0.093           | 32.84                 | 0.070         |

| ThreeHalves     |                          | <b>0.083</b>    | <b>30.96</b>          | 0.077         |

| This work       |                          | 0.133           | 76.36                 | <b>0.040</b>  |

| Half-Gates      | SKINNY-64-128            | 0.283           | 73.80                 | 0.194         |

| ThreeHalves     |                          | <b>0.153</b>    | <b>59.13</b>          | 0.096         |

| This work       |                          | 0.289           | 139.30                | <b>0.026</b>  |

| Half-Gates      | SKINNY-64-192            | 0.343           | 81.99                 | 0.246         |

| ThreeHalves     |                          | <b>0.166</b>    | <b>67.11</b>          | 0.118         |

| This work       |                          | 0.321           | 154.69                | <b>0.041</b>  |

| Half-Gates      | SKINNY-128-128           | 0.595           | 163.98                | 0.440         |

| ThreeHalves     |                          | <b>0.346</b>    | <b>126.66</b>         | 0.279         |

| This work       |                          | 2.281           | 2613.28               | <b>0.015</b>  |

| Half-Gates      | SKINNY-128-256           | 0.803           | 196.74                | 0.594         |

| ThreeHalves     |                          | <b>0.442</b>    | <b>154.71</b>         | 0.348         |

| This work       |                          | 2.563           | 3135.62               | <b>0.028</b>  |

| Half-Gates      | SKINNY-128-384           | 1.107           | 229.51                | 0.819         |

| ThreeHalves     |                          | <b>0.558</b>    | <b>182.77</b>         | 0.472         |

| This work       |                          | 2.841           | 3658.00               | <b>0.041</b>  |

| Half-Gates      | TWINE-128 [22]           | 0.202           | 75.52                 | 0.168         |

| ThreeHalves     |                          | <b>0.136</b>    | <b>60.40</b>          | 0.081         |

| This work       |                          | 0.191           | 108.21                | <b>0.059</b>  |

| Half-Gates      | TWINE-80                 | 0.187           | 68.80                 | 0.153         |

| ThreeHalves     |                          | <b>0.128</b>    | <b>53.99</b>          | 0.074         |

| This work       |                          | 0.199           | 99.04                 | <b>0.045</b>  |

ThreeHalves, each AND gate costs 6 calls to  $\mathcal{H}$  for garbling, 1.5 ciphertexts are sent, and 3 calls to  $\mathcal{H}$  for evaluation.

Table VI lists all studied primitives with the corresponding trade-off in garbling and communication cost, and evaluation improvement measured in the number of calls to  $\mathcal{H}$  and in the number of ciphertexts, respectively. We found three primitives in five configurations in total where our scheme improves in both garbling and evaluation cost over both reference garbling schemes<sup>6</sup>. In the remaining primitives and cases, projection gates trade off higher garbling and communication cost for faster evaluation performance. Note that for most primitives, the evaluation improvement is much higher than the additional communication cost. E.g., for Midori64, at a cost of slightly more garbling work ( $\approx 6\%$  more) and less than twice the number of sent ciphertexts, we improve the evaluation work by a factor of five. We detail the implementation approach with projection gates for the ciphers in Appendix B.

3) Experimental Results: Next, we experimentally compared the performance of four primitives in nine configurations in Half-Gates, ThreeHalves and our scheme. ThreeHalves has been implemented by Hamacher et al. [62] in the MOTION framework while Half-Gates and our scheme have been implemented in MP-SPDZ [63]. We also use the TMMO hash

function construction that is already used for Half-Gates in MP-SPDZ for our scheme. Our code is publicly available<sup>7</sup>. All used implementations already perform multi-threading<sup>8</sup> to accelerate the computation of gate garbling/evaluation as well as grouping together AES calls for improved pipe-lining behaviour. Batched/vectorized AES [64] may provide additional speed-up. The AES calls for our scheme are independent within each gate while the regular structure of the SPN primitives, e.g., all S-boxes are parallel, also allows simple batching for Half-Gates and ThreeHalves. We do not expect a drastic difference in how our scheme compares to Half-Gates and ThreeHalves when using vectorized AES. Table VII lists the garbling and evaluation time, and the circuit size. Garbling and evaluation time are wall-clock running times as reported by the frameworks, and circuit size is the number of bytes sent/received (whichever is higher) as reported by the frameworks. Garbler and evaluator were run on the same machine (6-core/12-threads AMD Ryzen 5 PRO 4650U 2.1 GHz with 8 GB RAM), connected over localhost, and limited to 4 threads each. We achieve a considerable speed-up in evaluation time of, e.g., factor 20 to 45 for AES. The expected trade-off of faster evaluation and larger circuit size is immediate for all implemented ciphers. Even though they were benchmarked in the same test environment and hardware, we observed differences in garbling and evaluation time between Half-Gates and ThreeHalves executions of the same circuit which cannot be explained by the differing number of hash function calls. We believe the observations are due to the implementation in the two MPC frameworks which have differing overhead.

#### C. Applications

In this section, we briefly describe two potential applications where fast evaluation of SPN primitives is crucial.

1) IoT-to-Cloud Secure Computation: In an Internet of Things (IoT) to Cloud scenario, the focus is on encrypting data at the source, specifically on the IoT devices, employing an SPN primitive and efficient distributed decryption in the cloud prior to privacy-preserving computation on the data (cf. [30, Application 4]). Such setup facilitates end-to-end secure data collection and processing. The distributed decryption should have low computation latency (and thus fast evaluation of the garbled circuit) in order to minimize the online phase of the combined protocol (distributed decryption and processing). With our proposed garbling scheme, IoT-friendly lightweight primitives can be used for efficient encryption on resourceconstraint devices and still obtain fast evaluation times for distributed decryption if garbled circuits are pre-processed.

2) Distributed Kerberos: The Kerberos authentication protocol is widely used, e.g., as one authentication method for Microsoft Windows. The key distribution center (KDC) plays a critical role in the architecture since it stores the secret keys of clients and service servers, and the secret key of the ticket-granting server (TGS). During the different stages of authentication, the KDC decrypts messages using the TGS secret key, and also encrypts messages with the client, TGS,

<sup>&</sup>lt;sup>6</sup>While the evaluation improvement is the goal of this work, the improvement in garbling time is caused by large, sub-optimal circuit representations of the 5-, 6- and 7-bit S-boxes for which, to the best of our knowledge, no smaller circuits are published in the literature.

<sup>&</sup>lt;sup>7</sup>https://github.com/KULeuven-COSIC/gc-fast-sbox-eval

<sup>&</sup>lt;sup>8</sup>Garbler and evaluator are restricted to 4 threads each.

and service server secret keys. Compromise of the KDC has devastating consequences as critical key material is leaked, which breaks all authentication goals. The security of keys can be increased by distributing the KDC among two servers G, E that each only stores a secret-share of each stored key, e.g.,  $k = k_G \oplus k_E$ . Consequently, the necessary encryption and decryption operations are computed using our garbling scheme where the two servers input their respective key share as private input. Clearly, clients only authenticate to the distributed KDC infrequently, allowing the garbling server Gto garble circuits for all required operations

- encryption of the client session key using a client key (as input),

- encryption of the ticket granting ticket using the TGS secret key (G can fix  $k_G$  in the circuit),

- encryption of the client-service session key using a service server's key (as input) and

- decryption of the client session-key using the TGS secret key (G can again fix  $k_G$  in the circuit)