# dCUDA: GPU Cluster Programming using IB Verbs

#### **Master Thesis**

Author(s):

Kuster, Lukas

**Publication date:**

2017

Permanent link:

https://doi.org/10.3929/ethz-a-010889936

Rights / license:

In Copyright - Non-Commercial Use Permitted

## dCUDA: GPU Cluster Programming using IB Verbs

Lukas Kuster

Master Thesis March 2017

Supervised by Prof. Torsten Hoefler Tobias Gysi

at the

Scalable Parallel Computing Laboratory

Department of Computer Science

ETH Zurich

### **Abstract**

Over the last decade, the usage of GPU hardware to accelerate high performance computing tasks increased due to the parallel computing nature of GPUs and their floating point performance. Despite the popularity of GPU accelerated compute clusters for high performance applications like atmospheric simulations, no unified programming model for GPU cluster programming is established in the community. dCUDA, a unified programming model for GPU cluster programming designed at ETH Zürich, is a candidate to fill this gap. dCUDA provides a device-side library for Remote Memory Access (RMA) of a global address space and supports fine-grained communication and synchronisation on the level of CUDA thread blocks. The dCUDA programming model enables native overlap of communication and computation for latency hiding and better utilisation of GPU resources by oversubscribing the system. dCUDA provides a well designed communication library and outperforms traditional GPU cluster programming approaches.

We extend the dCUDA library and improve the performance of the dCUDA programming model. New functionality enables new low latency synchronisation mechanisms and several optimisations increase the overall performance of dCUDA. The replacement of MPI based communication by a newly designed InfiniBand Verbs based network manager decreases dCUDA's remote communication latency by a factor of 2 to 3. Device local communication latency was improved by a factor of almost 3 thanks to a redesign of the dCUDA notifications system. Performance benchmarks demonstrate that the optimised framework using the InfiniBand network manager outperforms MPI based dCUDA implementations. Depending on communication patterns, it shows about 40% to 90% improved performance to traditional state of the art GPU cluster programming approaches.

## **Acknowledgements**

I would like to thank my advisors Tobias Gysi and Professor Torsten Hoefler of the Scalable Parallel Computing lab at ETH Zürich. The constructive discussions motivated my work and set me on the right tracks.

I would also like to thank Hussein N. Harake, the HPC system manager at CSCS. He set up and configured the test system on the *greina* cluster. His support on technical issues was vital for the success of the project.

Finally, I would like to thank Mark Silberstein, professor at Technion - the Israel Institute of Technology, for the exchange of ideas and the clarifications regarding GPUrdma.

## **Contents**

| LI | st of | Figure       | <del>)</del> \$      |       |       |   | VII |

|----|-------|--------------|----------------------|-------|-------|---|-----|

| Li | st of | Tables       | S                    |       |       |   | ix  |

| Li | st of | Listing      | gs                   |       |       |   | хi  |

| 1  | Intr  | oductio      | on                   |       |       |   | 1   |

| 2  | Bac   | kgrour       | ınd                  |       |       |   | 5   |

|    | 2.1   | CUDA         | A Programming Model  |       | <br>  |   | 5   |

|    | 2.2   | MPI .        |                      |       | <br>  |   | 6   |

|    | 2.3   | RDM <i>A</i> | [A                   |       | <br>  |   | 7   |

|    | 2.4   |              | Band                 |       |       |   | 7   |

|    | 2.5   | GPUD         | Direct               | <br>• | <br>• | • | 10  |

| 3  | Pro   | gramm        | ning Model           |       |       |   | 13  |

|    | 3.1   | dCUD         | DA Programming Model |       | <br>  |   | 13  |

|    | 3.2   | dCUD         | DA Code Example      |       | <br>  |   | 14  |

|    |       | 3.2.1        | Host Code            |       |       |   | 15  |

|    |       | 3.2.2        | Device Code          |       |       |   | 17  |

|    | 3.3   | dCUD         | DA Interface         |       | <br>  |   | 20  |

|    |       | 3.3.1        | Host API             |       | <br>  |   | 20  |

|    |       | 3.3.2        |                      |       |       |   | 21  |

|    |       | 3.3.3        | Interface Changes    | <br>_ | <br>  |   | 25  |

#### Contents

| 4  | Imp   | lementation                                     | 29 |

|----|-------|-------------------------------------------------|----|

|    | 4.1   | Architecture Overview                           | 29 |

|    | 4.2   | Network Manager                                 | 32 |

|    | 4.3   | Host-Device Communication                       | 35 |

|    | 4.4   | Notification Management                         | 36 |

|    | 4.5   | Notified Access                                 | 37 |

|    | 4.6   | Deployment                                      | 40 |

| 5  | Eva   | luation                                         | 45 |

|    | 5.1   | Test Environment and Timing                     | 45 |

|    | 5.2   | System Latency Benchmarks                       | 47 |

|    |       | 5.2.1 Network Communication Latency             | 49 |

|    | 5.3   | Bandwidth                                       | 50 |

|    | 5.4   | Case Study: Particles                           | 51 |

|    | 5.5   | Case Study: Stencil Program                     | 55 |

|    | 5.6   | Case Study: Sparse Matrix Vector Multiplication | 58 |

|    | 5.7   | Case Study: Power Iteration                     | 61 |

| 6  | Rela  | ated Work                                       | 67 |

| 7  | Con   | nclusions                                       | 69 |

| Bi | bliog | ıraphy                                          | 73 |

## **List of Figures**

| 2.1  | Fully connected system with different connection modes. Illustrations inspired |    |

|------|--------------------------------------------------------------------------------|----|

|      | by Subramoni et al. [25]                                                       | 1( |

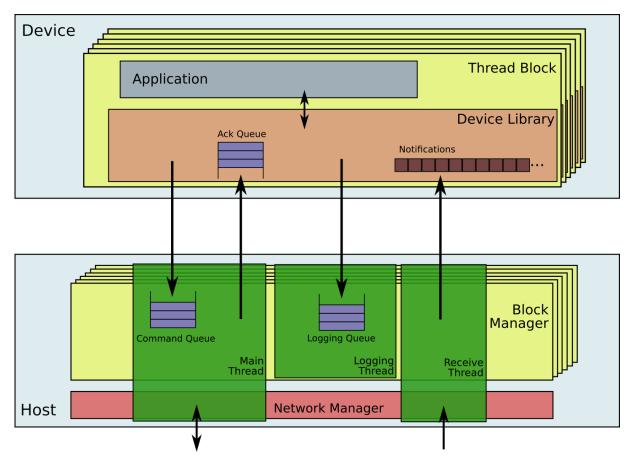

| 4.1  | dCUDA architecture overview: Device library instances with corresponding       |    |

|      | block managers in the host runtime system                                      | 30 |

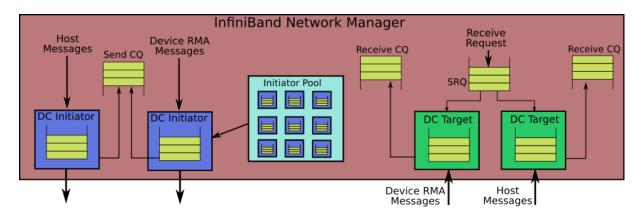

| 4.2  | InfiniBand Network Manager                                                     | 33 |

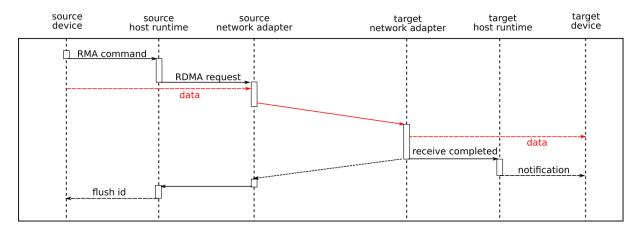

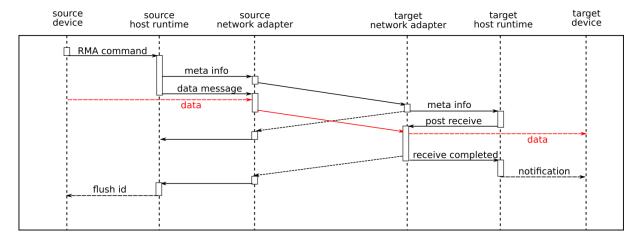

| 4.3  | Sequence diagram of notified memory put using InfiniBand Verbs                 | 39 |

| 4.4  | Sequence diagram of notified memory put using MPI                              | 40 |

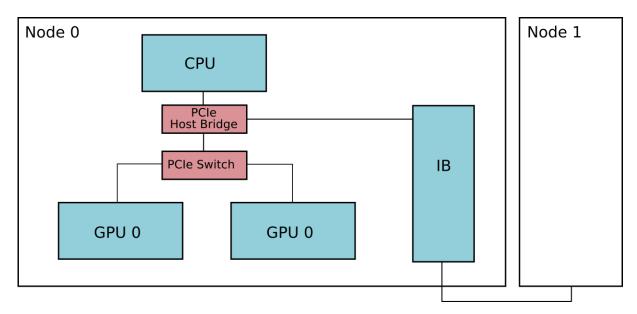

| 5.1  | Test system configuration                                                      | 46 |

| 5.2  | Particle algorithm communication pattern                                       | 52 |

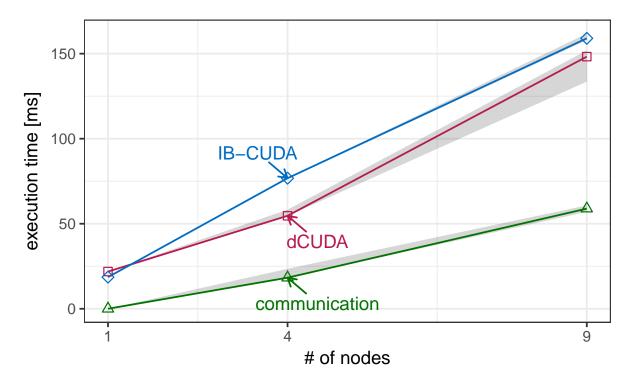

| 5.3  | Particles weak scaling with InfiniBand network manager                         | 53 |

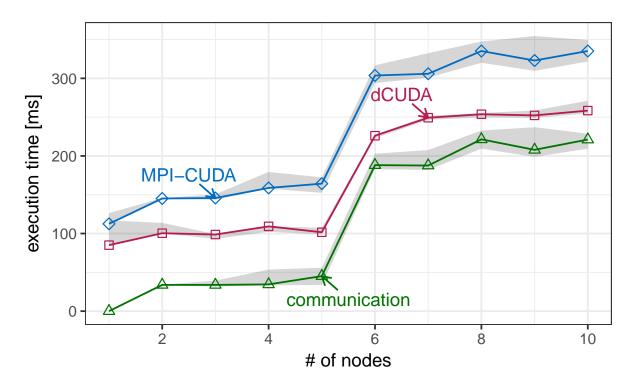

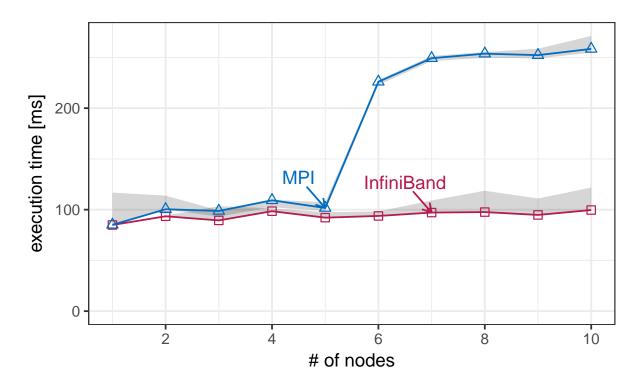

| 5.4  | Particles weak scaling with MPI                                                | 54 |

| 5.5  | Particles weak scaling with two versions of dCUDA                              | 55 |

| 5.6  | stencils weak scaling with InfiniBand network manager                          | 56 |

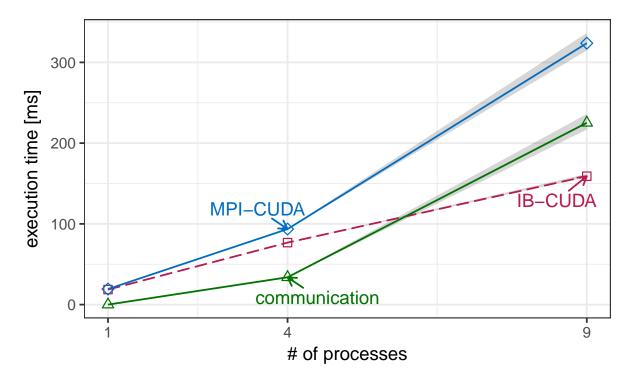

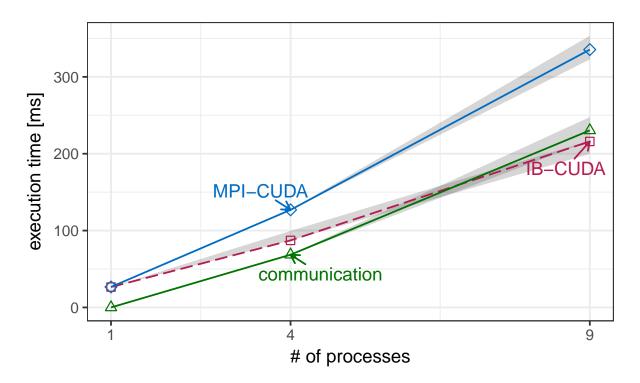

| 5.7  | Stencils weak scaling with MPI                                                 | 57 |

| 5.8  | Stencils weak scaling with two versions of dCUDA                               | 57 |

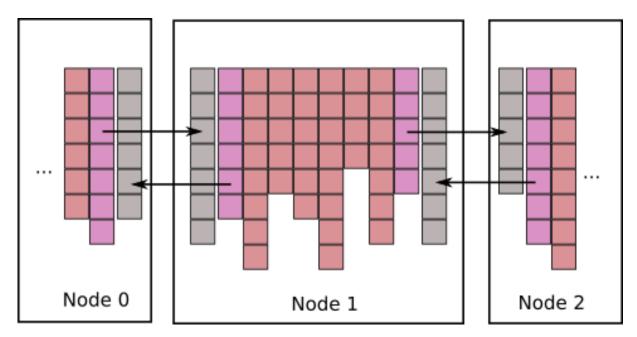

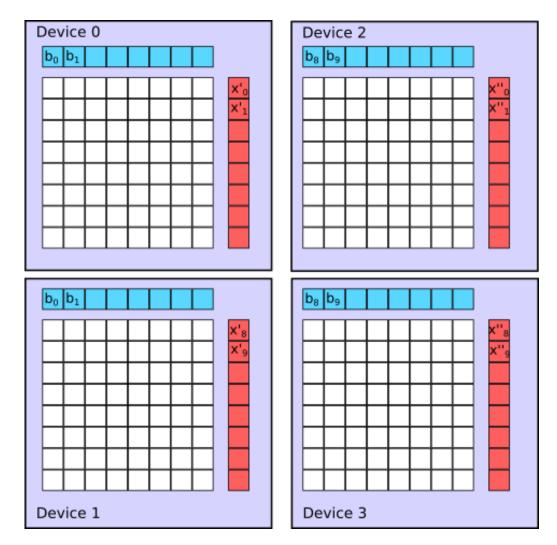

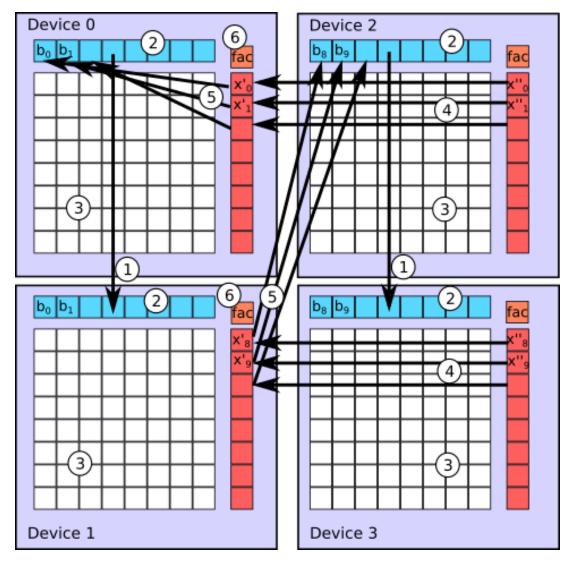

| 5.9  | Sparse Matrix Vector Multiplication domain decomposition                       | 59 |

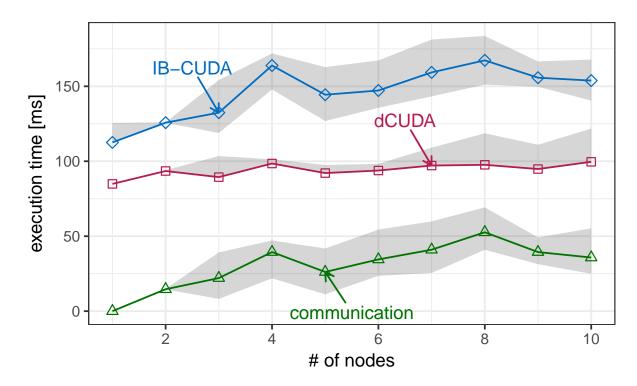

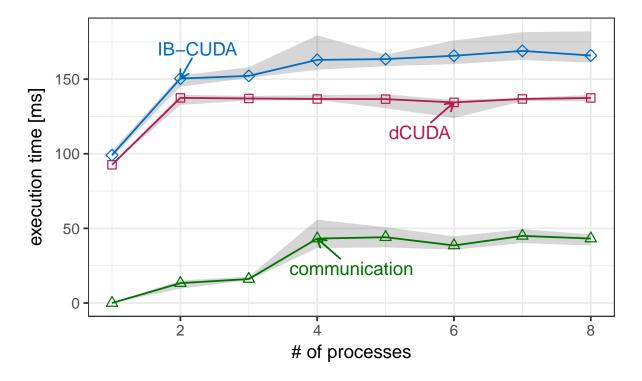

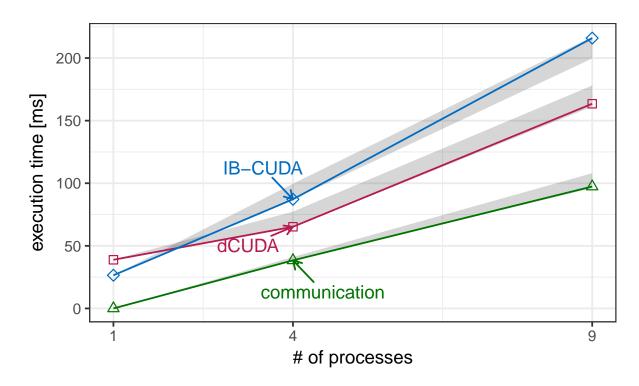

| 5.10 | Matrix vector multiplication weak scaling with InfiniBand network manager      | 60 |

| 5.11 | Matrix vector multiplication weak scaling with MPI and IB-CUDA as a reference. | 60 |

| 5.12 | Power Iteration work steps                                                     | 62 |

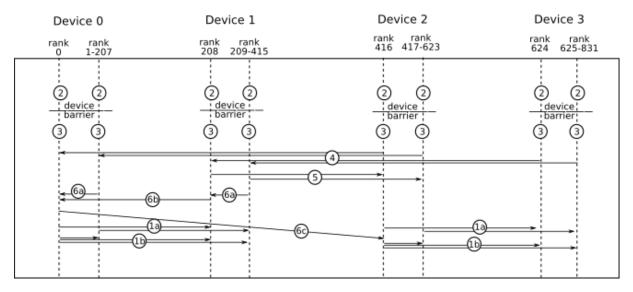

| 5.13 | Sequence diagram of the power iteration algorithm                              | 63 |

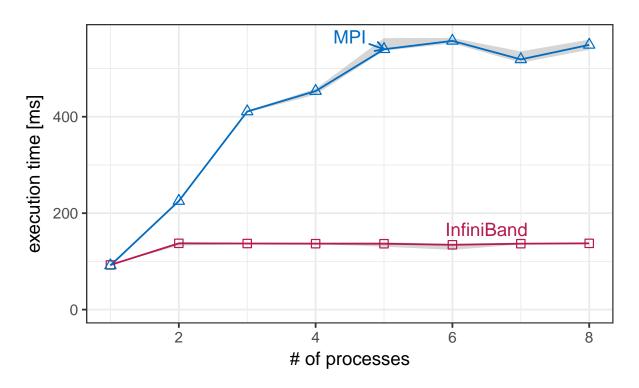

|      | Power iteration weak scaling with InfiniBand network manager                   | 65 |

|      | Power iteration weak scaling with MPI and IB-CUDA as reference                 | 66 |

## **List of Tables**

| 5.1 | Notified access and notify latency in $\mu s$                           | 47 |

|-----|-------------------------------------------------------------------------|----|

| 5.2 | Host-Device ping-pong on flag in host memory, flag in device memory and |    |

|     | using dCUDAs flagged queues. Results are round trip times in $\mu s$    | 48 |

| 5.3 | RMA ping-pong mean latencies in $\mu s$                                 | 50 |

| 5.4 | Bandwidth of one-directional notified accesses in GB/s                  | 51 |

## **List of Listings**

| 3.1 | Host Example Code: dCUDA initialisation and kernel invocation | 16 |

|-----|---------------------------------------------------------------|----|

| 3.2 | Device Example Code: Distributed reduction                    | 18 |

| 3.3 | DCuda Host API                                                | 21 |

| 3.4 | dCUDA device API, initialisation and timing                   | 22 |

| 3.5 | dCUDA Device API: Notified RMA                                | 23 |

| 4.1 | Initiator QP pool algorithm                                   | 34 |

|     | dCUDA wait notifications library function                     |    |

1

## Introduction

Supercomputers are specialized computers with tremendous computing power that are used by scientists and engineers to perform computationally intensive tasks like molecular dynamics [26], atmospheric models [3], turbulent combustion simulation [10] and other scientifically important tasks. They consist of up to thousands of individual computing nodes that are interconnected by a high speed network like Infiniband. To efficiently use all of the compute nodes, a programmer has to divide his problem into smaller sub-problems that are computed on individual nodes and minimise communication with other computing nodes. For example, in an atmospheric model, each computing node simulates the atmosphere for only a small region. But the state of the atmosphere at the border of a region depends also on the state of the neighbouring regions. Therefore, the state of the borders of the regions have to be exchanged with the neighbouring nodes in each simulation step. Programming models help the programmer to design the communication and synchronisation of the individual nodes that compute the problem in parallel. In this thesis, we analyse a new programming model called dCUDA (distributed Cuda) [8] designed for GPU accelerated computing clusters. We optimize the implementation described in [8] to get improved performance as we show in multiple case studies. We compare the optimized dCUDA to traditional programming models and show its advantages and disadvantages.

GPUs (Graphics Processing Units) became popular in the 1990s for 2D and 3D graphic rendering in personal computers. GPUs are specialised units that were originally designed to process 2D and 3D graphics. Graphics processing requires a high floating point operation throughput, which can be highly parallelised since each vertex or pixel can be computed independently. Scientists quickly realised that the floating point and parallelisation capabilities of GPUs are well suited to accelerate scientific computations. First, scientists used OpenGL to develop general purpose programs for GPUs, but this changed in 2007 with the introduction of the CUDA development environment and Tesla, the first general purpose GPU (GPGPU), by NVIDIA.

The programming model of CUDA allowed programmers to accelerate their high performance applications with the capabilities of GPUs with only little programming effort.

Today, supercomputers often heavily rely on the performance benefits of GPUs. Programmers use the CUDA programming model to manage CPU and GPU execution as well as memory transfers between CPU and GPU, which use different virtual memory spaces. In the CUDA programming model, the CPU initiates all memory transfers from and to GPU memory. The CPU also manages the execution on the GPU by starting so called CUDA kernels, which are special functions executed on the GPU. As opposed to the CPU, the GPU executes code not on a single thread, but up to thousands of threads execute the same code in parallel. This execution model is called Single-Instruction, Multiple-Threads architecture (SIMT). Threads are grouped into CUDA thread blocks. These thread blocks can access special block shared memory and have special synchronisation mechanisms. CUDA lacks any synchronisation primitives to synchronise threads in different thread blocks as it lacks a consistent memory model for global memory. Synchronisation and memory consistency is only guaranteed at the start and the end of a kernel function. Section 2.1 provides more detail on CUDA.

Compute clusters like supercomputers require another programming model that defines a standard for inter-node communication. The most common model is the Message Passing Interface (MPI), which defines a standard interface for message passing and remote memory access in any kind of network. MPI represents processes by ranks that can communicate with each other over a communicator using two-sided as well as one-sided message passing patterns. This model seems appropriate since the processes usually reside on different nodes and do not share the same memory space, therefore, messages have to be passed anyway. Two sided communication requires sender and receiver to be synchronised. The sender cannot complete a transaction without the receiver being ready to receive the message by calling the appropriate receive function. On the other hand, one sided communication does not synchronise source and target nodes. The target node does not participate in the communication at all. The sender copies data directly into the target's memory without any help from the target's CPU, using a Remote Memory Access (see section 2.3). For more information on MPI see section 2.2.

Modern high-performance computation applications often run on large compute clusters with GPU accelerated compute nodes. Programmers commonly use two programming models to program these kinds of applications. While the CUDA runtime can access GPU memory and execute code on the GPU, MPI is used to communicate with other nodes that participate in completing the task. Traditionally, an MPI-CUDA application alternately executes a CUDA kernel followed by a communication step using MPI on the CPU. The CUDA kernel computes the intermediate result of the current step using the massive parallelism of the GPU. At the end of the CUDA kernel execution, all threads are synchronised and the CPU initiates the necessary memory transfers of the intermediate result to and from other nodes. When the new data is read, the CPU can start the next CUDA kernel. Note that by using a CUDA aware MPI implementation, one does not need to copy the intermediate result to CPU in order to send it to another node. CUDA aware MPI can access GPU memory directly using a technology called GPUDirect (Section 2.5). In a typical MPI-CUDA application there is no local overlap of computation and communication. The CPU does not start to send or receive any data while the kernel is running and while the CPU is communicating with other nodes, the GPU is idle. Therefore, the computational power of the GPU is not optimally utilised by employing the traditional MPI-CUDA design.

The dCUDA programming model tries to combine the two models (MPI and CUDA) into one, opening up more optimisation possibilities and better utilisation of the GPU's resources. dCUDA provides message passing functionality on the level of CUDA blocks. Therefore, we do not have to finish a CUDA kernel before starting communication. This natively enables more fine-grained thread synchronisation and overlap of computation and communication, which speeds up the overall execution time. In the dCUDA programming model a rank represents a single CUDA block instead of the whole GPU device. Additionally, dCUDA enables local communication from one thread block to another block on the same device. This enables fine grained synchronisation of single blocks inside a kernel. dCUDA provides one-sided communication patterns on the level of thread blocks similar to the one-sided communication on the level of compute nodes that MPI provides. dCUDA combines remote memory access and notifications. The target of a remote memory access can be notified with a notification message, which can be queried by the receiver. The notification is very useful to synchronise the communication, which has to be done by additional two-sided messages in MPI. Notified remote memory access speeds up the execution time compared to traditional one-sided communication [2].

The dCUDA implementation from the original paper [8] uses MPI for communication. MPI is a high level interface for inter-node communication and abstracts system specific low level interfaces. Supercomputers often employ an InfiniBand high-performance network. The InfiniBand Verbs interface can be used to access the InfiniBand network stack. In this thesis we optimize dCUDA by replacing MPI entirely by InfiniBand Verbs. We aim at lower message latency due to reduction of potential MPI overhead. Section 2.4 provides more detailed information on InfiniBand Verbs. As not every system employs an InfiniBand network, the final implementation of dCUDA as described in this thesis includes a compile time switch to activate MPI. This enables running dCUDA on machines in a system without an InfiniBand interconnect.

In addition to the replacement of MPI by InfiniBand Verbs, we applied other performance and interface optimisations. We simplified the notification interface to enable performance optimisations in the notification handling process, we removed support for remote memory read accesses but added more functionality for memory put and for notify operations. The performance was improved by introducing multi-threading into the CPU code and a new timing infrastructure reduces programming effort for monitoring the execution time of GPU code.

In summary, we investigate different programming models used in high-performance computing applications on GPU accelerated computing clusters. In particular, we study the dCUDA programming model in detail and inspect and re-evaluate several design decisions, which in some cases got revamped in order to achieve better performance. We thereby focus on scalability and performance as well as usablility of the dCUDA library. We provide insights into the process of designing a programming model and implementing the dCUDA library and all of its challenges. Next, we evaluate the performance of the new implementation of dCUDA and compare it to the implementation of dCUDA as described in its original paper. We give a detailed analysis of the communication latencies in the system and report bandwidth for different scenarios. Finally, we will show four case studies. Each case study focuses on one particular mathematical problem, which is solved by a dCUDA application. In addition to the dCUDA implementation, each problem was also solved using traditional approaches using two models. One implementation uses MPI for its communication (MPI-CUDA) and a second implementation uses a InfiniBand Verbs based network manager instead (IB-CUDA). The four problems that we investigate in the

#### 1 Introduction

case studies are a Particle simulation, a stencil code, a sparse matrix vector multiplication, and a power iteration. The former three of these problems were already discussed in the original paper of dCUDA [8]. This thesis shows that the new dCUDA implementation is superior to the original one and outperforms traditional state of the art programming models. The power iteration algorithm was designed and implemented as part of this thesis and will be discussed in more detail than the other case studies. It shows new aspects of dCUDA and its advantages and disadvantages. dCUDA was developed on the *greina* cluster at the Swiss National Supercomputing Centre CSCS in Lugano using computing nodes that employ Nvidia K80 GPUs and use a InfiniBand high-performance interconnect.

## **Background**

During the last decade, developers and researchers discovered the potential of GPU accelerated programming for highly parallel programs. Today, modern HPC clusters and super computers often employ GPUs to accelerate their parallel tasks. Here we review the state of the art of GPU cluster programming and present the current networking technologies used in today's compute clusters.

#### 2.1 CUDA Programming Model

GPUs were designed to accelerate graphics processing and originally supported only graphics specific functions. In the late 1990s the GPUs became more programmable and could be used for general purpose programs. Initially, making use of the high floating point performance of GPUs was complex and required a lot of effort. In 2006 NVIDIA introduced CUDA (Compute Unified Device Architecture), a parallel computing platform and programming model for general purpose computing on GPUs. CUDA allows developers to write fast high level C code that is executed on the GPU [20, 21].

CUDA extends the C language with kernel functions that are executed on the GPU. Instead of being executed only by one thread like usual C functions, a CUDA kernel is executed N times in parallel by N distinct threads. Each thread executes the same instructions, whereas the only thing that distinguishes one thread from another are the thread and block indices. The threads are grouped into so called thread blocks. The threads in a block are organised in an up to three-dimensional grid and are identified by thread indices. Furthermore, the thread blocks are again organised in a grid of up to three dimensions. The programmer can decide on the dimensions of the thread hierarchy for each individual kernel call.

#### 2 Background

Each thread can access thread local memory, shared memory and global memory. Local memory is usually located in registers as long as there are enough registers to hold all local data. Therefore, memory access to local memory is the fastest option. Local variables are stored in thread local memory. Variables that are declared with the keyword shared are stored in shared memory that can be accessed by all threads in the same block. Shared memory access is much faster than global memory and should be used wherever it is suitable. To synchronize shared memory access, CUDA provides block synchronisation intrinsics like \_\_synchthreads () that act like a barrier for all threads in the block. Global memory has the longest access time but can be accessed by all threads in a kernel as well as by the CPU with special CUDA functions. Therefore, global memory is usually used to transfer the initial data to the GPU and the result back to the CPU. Global memory can be allocated by CUDA memory allocation functions. The CUDA memory model does not guarantee any memory consistency on global memory and different thread blocks may see memory accesses in different orders. To prevent read-write and other memory conflicts, one has to use atomic operations to concurrently modify global memory and memory fence instructions to maintain consistent memory. At the start and the end of a kernel execution global memory is consistent and CUDA thread blocks are synchronized. CUDA applications often run multiple kernels consecutively to get into a consistent state in-between kernel invocations.

The hardware of a modern Nvidia GPU consists of multiple multi-threaded streaming multiprocessors (SM). When a kernel is launched, thread blocks are distributed to SMs with available capacity. All threads of one thread block are executed on the same multiprocessor, but multiple blocks can be executed on the same multiprocessor concurrently. To manage hundreds of concurrent threads the multiprocessors have a special architecture called Single-Instruction, Multiple-Thread (SIMT) architecture. A multiprocessor executes threads in groups of 32 threads, which are called warps. The threads of a warp are always scheduled at the same time and simultaneously execute the same instructions. If some threads in a warp are in different branches, each branch is executed sequentially and threads that are not part of the current branch are deactivated. For the best performance, a programmer should always try to avoid warp divergence.

#### 2.2 MPI

Fast communication in a high performance cluster is essential for parallel programs. The Message Passing Interface (MPI) provides a high level interface for communication between processes running on different machines [18]. MPI does not define a protocol or implementation but defines a set of send/receive and collective communication functions. The interface abstracts all underlying network and protocol specific implementation details and the same code runs on any kind of system. Various MPI implementations exist that are continuously updated to support the most recent hardware and network technologies.

An MPI program starts N processes on M nodes. Each process has its own virtual memory. MPI groups all processes into a world communicator. The user can create additional custom communicators that contain a subset of the processes. Each process in a communicator has a unique rank index associated with that communicator. MPI provides several different functions to communicate with other ranks in a communicator, e.g. the straightforward send/receive

functions. MPI defines various collective functions that have to be called by all members of a communicator collectively. For example, the gather function can be used to collectively gather the individual results of all the nodes and collect them at the main process for further processing. For all these functions exist a blocking and a non-blocking variant. Blocking functions do not return until all participating ranks have called and finished the corresponding function, while non-blocking functions only initiate the transaction and do not wait for completion of the operation. This is useful as the corresponding processes can do other work while the data is transferred. The programmer has to keep in mind that send and receive buffers can not be used until the non-blocking operation has completed. To test if non-blocking operations have completed, one can call blocking wait routine or non-blocking test routines.

In addition to the two-sided communication, MPI-3 introduced one-sided communication patterns. One-sided communication does only need one process to actively participate in the communication. One-sided communication needs every rank in the communicator to create a shared window that specifies memory that is exposed to the other ranks in the communicator for remote memory access (RMA). After the window creation, each rank can put and get memory to and from a remote memory window without target process interaction. There is no synchronisation of the calling process and the remote process. Often additional two-sided messages are needed to synchronise the ranks after one-sided operations have completed.

#### **2.3 RDMA**

Remote Direct Memory Access or short RDMA is a technology that allows a host to access remote memory of another machine without participation of the remote CPU. In other words, it's a technique to implement RMA (Remote Memory Access). Note that RMA can also be implemented without RDMA. RMA is a concept that allows a process to access remote memory of a remote process. The remote process does not need to actively participate in the memory transaction. RMA does not define how it is implemented. A possibility would be that a background thread executes a routine that receives incoming messages and reads/writes local memory on the remote machine. RDMA implements RMA without any CPU usage on the target machine for the memory transactions.

A process can register local memory at a network adapter that supports RDMA. Registered Memory will be exposed to remote memory accesses and it is associated with a key that has to be sent to all peers before they can access this memory region. If a process knows the address and the key of a remote memory region, it can send a request to read or write that memory. The network adapter of the remote process will receive the request and will process it without interrupting or notifying the CPU. The network adapter can bypass the CPU and accesses the main memory directly using the local Direct Memory Access (DMA) engine.

#### 2.4 InfiniBand

InfiniBand (IB) is a high-bandwidth, low latency network architecture. It is used in high performance clusters and enterprise data centers. It competes with traditional networking architectures

#### like Ethernet.

In traditional network architectures, the network adapter resources are owned and managed by the operation system (OS). When a process needs to send a message, a context switch to the OS is needed. The OS moves the data from the virtual buffer space though the network stack onto the wire. InfiniBand on the other hand, directly provides the applications with the networking services without OS interaction. It provides protected channels that allow applications to use network resources directly while ensuring data isolation and protection [15]. The endpoints of these channels are called QPs (Queue Pairs). By accessing a QP, an application can accesses the resources of the network adapter card directly. On creation, the QPs are mapped to the applications user space. An application can own multiple QPs if it needs multiple channels. Usually a channel is bidirectional, which is the reason why a queue pair consists of a send queue and a receive queue. The InfiniBand Verbs API provides the user with functions to create and access all relevant resources to control the InfiniBand network adapter.

The send queue is used to post send requests. The InfiniBand HCA (Host Channel Adapter) polls and processes all the requests in the send queue. If an application expects to receive messages, it has to post receive requests on the receive queue. Whenever the HCA receives a message, it polls a receive request from the receive queue and uses the information from the request to process the receiving message. Both the send queue and the receive queue have a CQ (Completion Queue) associated with it. Whenever a request is finished, the HCA produces a completion entry and pushes it on the corresponding CQ. The application has to poll these CQs to know if a send operation has completed or to know if it has received a message.

InfiniBand provides two different messaging methods. First there are the traditional two-sided send/receive functions. The sender posts a send work request on the send queue of the QP. The work request contains the send buffer location. The HCA reads the buffer memory and puts it on the wire. The receiver has to pre-post a receive work request on the receive queue of the QP. The work request contains the location of the buffer where the message will be stored by the HCA. It is important that there is always a receive work request in the receive queue when such a message arrives because otherwise, the HCA does not know how to process the data and the QP goes into an error state. The receiver can poll the CQ of his receive queue to get informed about incoming messages.

The second data transfer method is called RDMA write and RDMA read (Remote Direct Memory Access). When using this method, only the CPU of the initiator of the data transfer is involved. The initiator posts a RDMA write or read work request giving the local buffer location as well as the remote buffer location. On the receiving side, the HCA directly writes or reads at the specified memory location without interrupting or notifying the CPU of that node. To prevent memory corruption by remote applications, RDMA functions can only access remote memory that was registered using the InfiniBand Verbs API. Registered memory is associated with a remote key and a local key for remote and local accesses. Remote memory can only be accessed if the application knows the remote key of that memory region. The remote keys have to be exchanged at application start and prevent unauthorized memory accesses.

The target of a RDMA write or read is not notified and the process does not know when data is transferred. An additional round trip time is needed to synchronize the processes before or after a set of RDMA operations. As stated by R. Belli and T. Hoefler, notified RMA accesses can provide up to 50% application speedup for small messages [2]. InfiniBand provides a function

that in addition to a RDMA write also notifies the target process. This function called *RDMA* write with immediate does the same as RDMA write but also sends a 32 bit immediate value within the message. The target process can poll the receive CQ to get the immediate value as soon as the RDMA write is completed. A similar function for RDMA reads does not exist in the InfiniBand Verbs standard.

InfiniBand supports several different transport protocols. The most common one is the RC (Reliable Connection) transport. RC QPs are endpoints of a static communication channel. They are comparable to TCP sockets, although not quite the same. Every message sent on a reliable channel is followed by an acknowledgement message. A send-request can only be completed when the acknowledgement was returned. In a large network, as they are common in compute clusters, each process needs to maintain a large number of QPs to get full connectivity, which needs a lot of resources on each node. For example, a system with N nodes and P processes on each node needs  $N \cdot P \cdot P$  QPs on each node to have full connectivity. RC transport has good performance but for a system with millions of processes, it consumes a lot of resources.

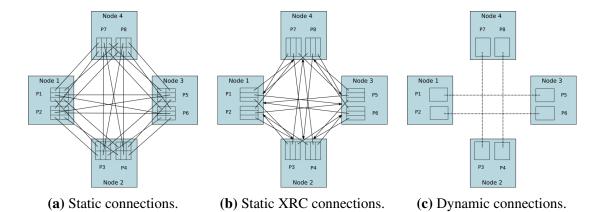

The second transport protocol is the UC (Unreliable Connection) transport. A UC QP is associated with exactly one other QP, just like RC. The only difference is that the connection is not reliable and packets can be lost. Figure 2.1a depicts the static RC or UC channels of a fully connected system of four nodes with 2 processes each. Intra-node communication is not shown. Each process has a channel to every other remote process.

The third type of supported transport protocol is UD (Unreliable Datagram) transport. This protocol is similar to UDP. A UD QP does not instantiate a connection to another QP unlike RC QPs. The destination of each individual message has to be stated. A single UD QP can be used to send messages to all other processes in the system. Therefore, the resource demands in a large system is constant per process. The drawback is that UD transport does not guarantee that the messages reach their targets. If a reliable transport is needed, it has to be implemented by the programmer, which degrades the performance of the network significantly. Figure 2.1c shows a system using UD transport. Channels are dynamic and can change its target at any time.

In addition to the three initial transport protocols, new types were introduced as InfiniBand evolved [16]. The XRC (extended Reliable Connected) transport protocol [11] tries to reduce the number of QP needed for all to all communication in a large cluster with many processes per node, while still being reliable. XRC significantly reduces the number of QPs from  $N \cdot P \cdot P$  RC QPs to  $N \cdot P$  XRC QPs per node. Each XRC QP connects to a XRC target. The target can be associated with all the QPs on that node. This means that a single QP can send packets to all processes of a single node, not only to a single process. Scalability of XRC transport is better than RC for clusters with a lot of cores but still a lot of resources are needed for large compute clusters with a lot of nodes. Figure 2.1b shows the channels of the XRC protocol. QPs are connected to target nodes instead of individual target QPs.

The last transport protocol introduced into InfiniBand is the DC (Dynamically Connected) transport. DC transport reduces the resource usage even further. It tries to combine the advantages of reliable connections and unreliable datagrams. Each process in the system needs at least one DC initiator QP for sending packets and a DC target to receive incoming packets. When a process needs to send a packet, it identifies the target of the packet and the DC QP dynamically

#### 2 Background

**Figure 2.1:** Fully connected system with different connection modes. Illustrations inspired by Subramoni et al. [25].

connects to the corresponding DC target. The DC initiator and the DC target initiate a reliable connection for the time packets are sent from the initiator to the target. The connection remains active as long as the initiator sends packets to the same target. The connection gets torn down whenever the initiator changes its target or after a short timeout. The performance of the DC transport is comparable to the performance of RC transport but adds an overhead of roughly 100 nanoseconds to the latency for establishing the dynamic connections [25]. A single DC Initiator can dynamically connect to all targets in the system. Thus, each node in a compute cluster with P processes per node needs only P DC initiators and targets to achieve full connectivity. Therefore, the DC transport protocol scales well for large compute clusters with thousands or millions of nodes as the resource consumption of InfiniBand remains constant in the number of nodes. 2.1c depicts the dynamic connections of the DC transport protocol. Like UD transport, channels are dynamically created and destroyed whenever needed.

#### 2.5 GPUDirect

GPUDirect is a family of technologies introduced by Nvidia for their general purpose GPUs [19]. First, it introduced a technology to support accelerated communication with third party PCI-E devices via shared pinned host memory. This accelerated communication by getting rid of a memory copy in host memory from the CUDA driver buffer into a third party driver buffer like the InfiniBand driver. Memory staging into shared host memory was still necessary. In 2011 Nvidia introduced GPUDirect peer to peer, which supports direct memory access between GPUs on the same PCI-E root complex. This allows memory transfers without passing the host main memory, removing another memory copy. In 2013 GPUDirect RDMA was introduced, which enabled third party drivers to directly access GPU memory. With GPUDirect RDMA a third party driver like the Mellanox InfiniBand driver can directly access GPU memory and bypasses host main memory altogether.

Mellanox supports GPUDirect RDMA in its drivers since the introduction of the Mellanox ConnectX-3 HCA [17]. This allows the InfiniBand HCA to directly access GPU memory and completely bypass host main memory. The system requires Mellanox OFED version 2.1 or

higher and the *nv\_peer\_mem* plugin to be enabled in order to work. The InfiniBand driver will automatically distinguish host memory and GPU memory and will automatically use GPUDirect RDMA in the latter case if the system is properly set-up.

Several MPI implementations support GPUDirect RDMA, which is often referred to as CUDA-aware MPI. OpenMPI support CUDA-awareness since version 1.7.0. To make use of the features of GPUDirect, one has to enable it by passing the appropriate parameters to *mpirun*, as it is disabled by default [24]. OpenMPI will use GPUDirect only for small packets smaller than 30'000 bytes by default. Larger packets are pipelined and staged through host main memory because it yields better throughput. The point where the protocol switch happens can be adjusted with another MPI parameter.

GPUDirect was designed for direct access of GPU memory from third party devices. The same GPUDirect API can be used to map the GPU memory to the CPU. Gdrcopy is an open-source library based on GPUDirect RDMA for low latency GPU memory copy [22]. It gives the user the ability to map GPU memory to user-space, which then can be used as if it were host memory. As a consequence, gdrcopy can be used to copy data from and to GPU memory with low overhead giving a low latency alternative to the CUDA memory copy routines. Initially, the GPU memory has to be pinned to host memory, which is expensive. When the memory is pinned, all memory copies have a low latency which is essential for a GPU messaging interface in a compute cluster controlled by the CPU as described in this thesis.

## **Programming Model**

dCUDA defines and implements a programming model for multi-GPU applications with communication on the level of GPU thread blocks. We define the model here in more detail and we present a short program example to show how dCUDA can be used to program multi-GPU applications with fine-grained communication and synchronization patterns. Further, we discuss the interface and present all functions provided by the dCUDA library. We will also discuss in detail all changes in the library interface made since the original publication of dCUDA [8].

#### 3.1 dCUDA Programming Model

dCUDA combines the programming models of CUDA and MPI. Both models are described in Sections 2.1 and 2.2 respectively. dCUDA kernels are launched with a user configurable number of thread blocks. The threads are organised in one dimension unlike CUDA kernels, which have up to three dimensions. Support for higher dimensional thread hierarchies might be added in future works on dCUDA. dCUDA does not allow to directly control the number of thread blocks a kernel launches. It only launches as many blocks as it is able to run in parallel on the streaming processors of the GPU or a maximum of 208 thread blocks. When CUDA launches more blocks than it could possibly run in parallel, some of them are postponed and are started when other thread blocks have finished execution and freed its resources. This would imply a major problem for dCUDA as inter-block synchronisations lead to potential deadlocks. The user can control the number of thread blocks indirectly by adjusting the number of threads per block or by limiting each thread to a maximum number of registers by setting the compiler flag *-maxrregcount*. Limiting register usage per block allows more blocks to run in parallel but execution might be a bit slower as some local variables are stored in global GPU memory instead of registers. Newer GPU devices that support preemption of thread blocks would relax the

restrictions on the number of spawned thread blocks. The current implementation of dCUDA is designed for non-preemptive GPUs.

In the MPI programming model, each MPI process can communicate with all other processes in a communicator and all processes are identified by a rank index. dCUDA uses fine-grained communication on the level of GPU thread blocks. Therefore, the dCUDA model identifies each thread block of its GPU device as a rank. In the remainder of this work we use the terms thread block and rank interchangeably in the context of dCUDA. dCUDA allows to send data and synchronise with any rank in the system, whether it is a local rank on the same device or a remote rank on another node.

MPI creates a global communicator on initialisation to communicate with other ranks in the system. The user can then create other communicators that consist only of a subset of all the ranks to form smaller communication groups. dCUDA provides two default communicators. First, the global communicator indicated by DCUDA\_COMM\_WORLD, which includes all ranks in the system and allows any two rank to communicate with each other. Additionally, there is a communicator denoted as DCUDA\_COMM\_DEVICE, which includes all local ranks of the same device. Currently, dCUDA does not support custom communicators. Support for it might be added in future versions of dCUDA.

dCUDA's communication model is based on notified RMA [2]. It is similar to one sided communication of MPI but with native support for target notification [7]. Communication requires creation of a memory window in one of the communicators. All ranks of the communicator have to collectively create a memory window that exposes the corresponding memory to remote accesses by other ranks in the same communicator. Any rank in that communicator can then access the memory windows of the other ranks and modify its content. Each put operation can be accompanied by a notification to let the owner of the memory window know that its memory was modified and to synchronise the ranks. Memory windows of ranks on the same device are allowed to overlap. dCUDA is optimised to perform no memory copy if the source and the target buffers point to the same memory location. Ranks that need data from another rank can wait for notifications with specific tags. When the data arrives, the receiver is notified and continues its work.

#### 3.2 dCUDA Code Example

To illustrate the dCUDA programming model and its API, we present a small dCUDA code example. The example illustrates how to initialise dCUDA, how to load data to the GPU and back to the CPU and finally how to write a simple dCUDA kernel with fine grained communication and synchronisation. The simple example code provided here implements reduction. An array of random values is generated and all dCUDA ranks in the system calculate the sum of all values in parallel using reduction. The asymptotic runtime of this simple algorithm is  $\mathcal{O}(\log n)$ .

#### 3.2.1 Host Code

Listing 3.1 shows the host code that is executed by the CPU. The code initializes dCUDA and generates the initial data that will be summed up by the dCUDA kernel. After launching the kernel, it will report the result and the execution time of the algorithm. Following, we will explain each step of the code in more detail.

First, the code includes all necessary packages and defines a custom struct *user\_data* on line 1 to 12. The struct is later used to load data to the GPU. The user can add as many fields to the struct as necessary. In this example the field *data* will point to an array in GPU memory that will hold the initial data and the intermediate results of the algorithm. The *buffer* points to another array in GPU memory that is used as a receive buffer for incoming values from other ranks. Note that the buffer will be shared by all ranks on the same device and therefore has to be properly managed to avoid race conditions. The field *is\_leader* indicates that this is the root device in the system. The double *result* will hold the result of the algorithm. Note that the struct can be used to load data to the GPU as well as copying the result back to the CPU after kernel execution.

On program start, the code initializes dCUDA with the function dcuda\_host\_init() on line 17. We pass the dCUDA kernel we want to execute later to the function and the number of threads per block, which is 128 in this example. dCUDA does not allow to directly control the number of blocks that are launched but it gives users the opportunity to query all relevant information so that they can design their algorithm appropriately. The function dcuda\_host\_get\_rank\_info() gives all relevant information about the configuration of the system. In the code example on lines 22 to 26 we read the number of ranks on the local device, which is equal to the number of thread blocks that will launch, and the total number of ranks in the system that includes all other dCUDA processes that are started in parallel.

Next, we allocate and initialize the arrays we need for the algorithm. The struct *user\_data* does only hold pointers to the array but not the arrays themselves. Thus, we have to first allocate them in GPU memory. We decide that each thread of the device will have one value and set the size of the array appropriately. We use <code>cudaMalloc()</code> on line 30 to allocate memory on the GPU. Note that we want the two arrays to be in consecutive memory for our algorithm. Therefore, we allocate both arrays with only one call to <code>cudaMalloc</code>. In the next step, we initialize the data on lines 34 to 37. We allocate another array in main memory, initialize the array with random numbers, and copy the data to the GPU using <code>cudaMemcpy()</code> on line 40.

After having allocated the memory we need and copied the initial data to the GPU, we are ready to launch the actual dCUDA kernel on the GPU on line 44. The function dcuda\_host\_run() copies the userdata as defined in the struct *user\_data* to the device, launches the kernel, and copies the userdata back to main memory. The struct holds any result that the kernel has set without the need to manually copy it. The function dcuda\_host\_run() only returns when the kernel finished execution.

After the kernel execution, the main process reports the result of the algorithm, which is stored in the *result* field of the *user\_data* struct. On lines 47 to 51 we get the execution time of the algorithm (excluding any initialisation time) by calling dcuda\_host\_get\_timings(), which returns all timing results done during kernel execution and we report the result. See the

```

#include <cstdlib>

#include <iostream>

#include "dcuda_host.h"

3

#include "dcuda_device.cu.h"

#define THREADS_PER_BLOCK 128

struct user_data

6

8

double *data;

double *buffer;

bool is_leader;

10

double result;

11

12

};

13

int main(int argc, char **argv) {

14

//dcuda initialization

15

dcuda_host_context_handle dcuda_host;

16

dcuda_host_init(argc, argv, &dcuda_host, kernel, THREADS_PER_BLOCK);

17

user_data userdata;

18

19

//rank information

20

dcuda_rank_info rank_info;

21

dcuda_host_get_rank_info(dcuda_host, &rank_info);

22

int local_comm_size = rank_info.rank_responsible;

23

int world_comm_size = rank_info.rank_count;

24

userdata.is_leader = (rank_info.node_index == 0 &&

25

rank_info.device_index == 0);

26

27

//data allocation

28

int size = local_comm_size * THREADS_PER_BLOCK;

29

cudaMalloc(&userdata.data, 2 * size * sizeof(double));

30

userdata.buffer = &userdata.data[size];

31

32

//data initialization

33

double *init_data = (double*) malloc(size * sizeof(double));

34

for (int i = 0; i < size; i++) {

35

init_data[i] = std::rand();

36

37

38

//copy data to device

39

40

cudaMemcpy(userdata.data, init_data, size * sizeof(double),

cudaMemcpyHostToDevice);

41

42

//run dcuda kernel

43

dcuda_host_run(dcuda_host, &userdata, sizeof(userdata));

44

45

//report result

46

if (userdata.is_leader) {

47

double time = dcuda_host_get_timings(dcuda_host)[0];

48

std::cout << "Sum = " << userdata.result << std::endl;</pre>

49

std::cout << "Computation Time: " << time << " ms" << std::endl;</pre>

50

51

}

52

//cleanup

53

free(init_data);

54

cudaFree (userdata.data);

55

dcuda_host_finish(dcuda_host);

56

return 0;

57

58

}

```

**Listing 3.1:** Host Example Code: dCUDA initialisation and kernel invocation.

device code for an example on how to start/stop a timer.

We finish our code example by deallocating the memory used and clean up dCUDA by calling dcuda\_host\_finish() on lines 54 to 57.

#### 3.2.2 Device Code

The device code running on the GPU does the actual work. The kernel code showed in Listing 3.2, executes when the function dcuda\_host\_run() is called. dCUDA kernel code is always simultaneously executed by many threads in parallel, like in the CUDA programming model. In the following, we describe the kernel example code step by step to see the important features of dCUDA in action.

At the beginning of every dCUDA kernel we have to initialize the dCUDA device library (line 6). First, we declare a dcuda\_state in shared memory (indicated with the keyword \_\_shared\_\_). It is important to note that the dcuda\_state must be in shared memory as it holds all dCUDA internal data private to each thread block and shared by the threads of the thread block. Next, we initialize the dcuda\_state by calling the function dcuda\_gpu\_init(). This function must be called prior to any other dCUDA call.

After the initialisation, we query the size of the two default communicators and what rank index we have in the corresponding communicators on line 8 to 11. For now, the communicators DCUDA\_COMM\_WORLD and DCUDA\_COMM\_DEVICE are implemented, which contain all ranks in the whole system and all ranks of the local device respectively. The rank index in the device communicator is always equal to the block index of that thread block (blockIdx.x) and the size of the device communicator is equal to the CUDA grid size (gridDim.x). The query dcuda\_comm\_rank() returns a different result for each thread block. The rank in the world communicator is unique for each thread block across the whole system.

In the host code in the Listing 3.1 we stored the important information in the struct *user\_data*, including a pointer to our data array. To access this data on the device, we call dcuda\_get\_data() on line 13, which gives us a pointer to the user data.

Before starting the algorithm, we have to create a memory window, which is used for communication with other ranks. dcuda\_win\_create() has to be called by all ranks in the communicator collectively like we do on lines 17,18. The window base in memory and window size can be different for each rank and ranks that do not participate in the communication can set the size to zero. Source and destination buffers of RMA operations have to reside inside of the created window. In our example, we create only one window in the world communicator. A window in the world communicator can also be used for local communication but a window in the device communicator can not be used for global communication. We create a window that spans both arrays: the *data* array holding our data, as well as the *buffer* array used as a receive buffer. Note that we allocated these arrays in consecutive memory in the host code.

Before starting the actual algorithm, we start a timer to measure the execution time of the algorithm on line 21 ( $dcuda_start_cpu_timer()$ ). At the end of the algorithm on line 48 we stop the timer. The host can later query the timing result with a call to  $dcuda_host_get_timings()$ .

```

_global___ void kernel(dcuda_context_handle dcuda)

2

3

int size, rank, local_size, local_rank;

4

__shared__ dcuda_state gst;

dcuda_gpu_init(dcuda, gst);

6

dcuda_log log = dcuda_log_get(gst);

dcuda_comm_size(gst, DCUDA_COMM_WORLD, &size);

8

dcuda_comm_rank(gst, DCUDA_COMM_WORLD, &rank);

dcuda_comm_size(gst, DCUDA_COMM_DEVICE, &local_size);

10

dcuda_comm_rank(gst, DCUDA_COMM_DEVICE, &local_rank);

11

user_data *data;

12

dcuda_get_data(gst, (void**)&data);

13

14

//create windows

15

dcuda_win win;

16

dcuda_win_create(gst, DCUDA_COMM_WORLD, data->data,

17

2 * local_size * blockDim.x * sizeof(double), &win);

18

19

//timing

20

dcuda_start_cpu_timer(gst);

21

22

//block reduction

23

if (threadIdx.x == 0) {

24

for (int i = 1; i < blockDim.x; i++)

25

data->data[local_rank * blockDim.x] +=

26

data->data[local_rank * blockDim.x + i];

27

}

28

}

29

30

//global reduction

31

int offset = (local_size * blockDim.x + rank) * sizeof(double);

32

for (int step = 1, round = 0; step < size; step *= 2, round++)

33

34

{

35

int range = 2 * step;

bool send = rank % range == step;

36

bool recv = (rank % range == 0) && (rank + step < size);

37

if(send){

38

dcuda_put_notify(gst, win, rank - step, offset, sizeof(double),

39

40

&data->data[local_rank*blockDim.x], round % 256);

41

if(recv){

42

dcuda_wait_notifications(gst, round % 256, 1);

43

data->data[local_rank * blockDim.x] += data->buffer[rank+step];

}

45

46

47

dcuda_stop_cpu_timer(gst);

48

if(rank == 0){

49

50

data->result = data->data[0];

51

log << "result = " << data->result << log.flush;</pre>

52

53

//cleanup

54

dcuda_win_free(gst, win);

55

dcuda_gpu_finish(gst);

56

57

```

**Listing 3.2:** Device Example Code: Distributed reduction

At the start of our algorithm each thread owns a single value located at data->data[local\_rank \* blockDim.x + threadIdx.x]. The algorithm sums all initial values of the data array. In the end, thread 0 of rank 0 will have the sum of all values stored in its memory location. We achieve this by doing a reduction on a binomial tree in two phases. In the first phase, each rank sums up the values of all its threads on lines 24 to 29. This phase does not need dCUDA specific functions and we use a simple but inefficient approach to do it. We use the threads in each block with index 0 to sum up all values of the block. A more efficient variant can be found in the Nvidia developer blogs [14]. At the end of this phase, the first thread of each rank has the sum of all the values in his block.

The lines 31 to 46 show the second phase of the algorithm. The phase has a logarithmic number of steps. In the first step, all ranks with odd rank index send their value to their neighbour with smaller rank index. The ranks with even index wait for the value and add it to their own value. In the next round, the ranks that have sent a value remain inactive. Half of the ranks that received a value in the previous round will now become senders and the other half remain receivers. After  $\log n$  rounds rank 0 is the only active rank left and it will hold the result of the reduction.

Now, we look into how data can be sent with dCUDA. With dcuda\_put\_notify() we can take memory from our window and put it into the window of a remote rank. The remote rank is notified once the data has arrived. On line 39 we pass the following arguments to the function: the state of the rank, the memory window to use, the target rank index, the offset from the target window base where the data will be written, the size of the data, the pointer to the local data buffer (which has to be inside the specified window), and a notification tag. The offset in the example equals the location data->buffer[source\_rank] in the target window. Note that the tag value has to be positive and less than 256. Section 3.3.3 discusses the design decision to limit the tag size to 8 bits. dCUDA automatically detects if the target rank is located on the same device or on a remote device and acts accordingly.

dCUDA uses RMA to send data, which means the sender can modify remote memory directly. Thanks to the dCUDAs notification system, the receiver is notified whenever its memory was modified and new data is ready to use. If a rank needs data from another rank, it can wait for incoming notifications by using dcuda\_wait\_notifications(). In our example we wait at line 43 for a single notification with the tag round % 256. Note that the function can also be used to wait for multiple notifications with the same tag, e.g. a rank waits for notifications from multiple sources. The function blocks until enough notifications have arrived or returns immediately if enough notifications have been received previously. We know that after receiving the notification, the corresponding data is ready. Therefore, the receiver rank can add the received value to its own value on line 44.

Finally, we print the result directly to the console on line 51 with the help of the *dcuda\_log* object. Then, we free the dCUDA window and finish the kernel by calling dcuda\_gpu\_finish() to clean up dCUDA resources on lines 55 and 56.

It has to be mentioned that the code in Listing 3.2 does not yield optimal performance but it shows the basic building blocks of the dCUDA programming model. The code has more remote accesses and memory copies than necessary. An optimised version would divide the last phase into two phases: one that reduces the result on the local device without the use of memory copies (dCUDA provides the function dcuda\_notify() for that case). In the last phase,

only one rank per device is active and a minimal number of remote accesses are performed to get the final result.

#### 3.3 dCUDA Interface

The host API is mostly used to initialize dCUDA and launch the dCUDA kernel. The device API provides functions to create memory windows and several functions to perform RMA operations and synchronisation mechanisms.

#### 3.3.1 Host API

dCUDA simultaneously launches multiple processes on multiple nodes in the system. One process manages exactly one GPU device. Nodes with more than one GPU device can launch up to as many processes as they own. The initialisation of the dCUDA host sets up and prepares all communication channels needed by dCUDA. Also, the dCUDA kernel is prepared for launch.

Listing 3.3 shows the interface of the host. The type <code>dcuda\_host\_context\_handle</code> points to the dCUDA context, which holds all resources needed by the host to perform any dCUDA related operation. All dCUDA host functions require a context handle to be passed as an argument. The type <code>dcuda\_context\_handle</code> is a pointer to the dCUDA resources needed by the device. The type <code>dcuda\_kernel\_t</code> defines the signature of the dCUDA kernels that the users implement. Any dCUDA kernel must have a single parameter, which is a dCUDA device context.

**dcuda\_host\_init** initialises dCUDA. The program parameters, which include dCUDA run information, are passed down to dCUDA with the first two parameters of *dcuda\_host\_init*. The function outputs a *dcuda\_host\_context\_handle* in the third parameter, which has to be passed to any subsequent dCUDA call. Additionally, the function requires a pointer to the dCUDA kernel and the number of threads per rank to properly prepare the launch of the kernel.

**dcuda\_host\_get\_rank\_info** can be used to query the launch configurations of dCUDA. It returns a *dcuda\_rank\_info* struct that holds all relevant information that the user needs to prepare the data for the kernel launch. Lines 7 to 15 in the Listing 3.3 show all fields of the rank info struct.

**dcuda\_host\_run** launches the dCUDA kernel previously passed to dCUDA. Optionally, one can pass a pointer to some user data to the function. The data will be copied to the device where it can be accessed with the device function *dcuda\_get\_data*. The function will copy the data back from GPU memory to the same host memory after the kernel execution. Therefore, all the changes made by the device will be visible to the host. The function blocks during kernel execution and it returns the total execution time in milliseconds of the dCUDA kernel.

**dcuda\_host\_get\_timings** returns a vector containing the timing information collected using the device functions *dcuda\_start\_cpu\_timer* and *dcuda\_stop\_cpu timer*.

**dcuda\_host\_finish** has to be called at the end of the program to clean up all resources and tear down open connections. A dCUDA host context can not be used for any dCUDA calls after a call to *dcuda\_host\_finish*.

```

typedef struct dcuda_host_context* dcuda_host_context_handle;

typedef struct dcuda_context* dcuda_context_handle;

typedef void (*dcuda_kernel_t) (dcuda_context_handle);

struct dcuda_rank_info

5

6

int rank_count;

///< total number of ranks

7

int rank responsible; ///< number of ranks I own

8

9

int rank_start,

int device_count;

int device_index;

int device_index;

int node_count;

int node_count;

int node_index;

int process_count;

int process_index;

int process_index;

int process_index;

int process_index;

//< index of my node

index of my processes

int process_index;

//< index of my process</pre>

///< number of active devices on this compute node

10

///< my device index on the node

11

12

13

15

};

16

17

18

void dcuda_host_init(int argc, char *argv[],

19

dcuda_host_context_handle *ctx,

20

dcuda_kernel_t kernel,

21

int threads_per_rank);

23

void dcuda_host_get_rank_info(dcuda_host_context_handle ctx,

24

dcuda_rank_info *rank_info);

25

26

double dcuda host run(dcuda host context handle ctx,

27

void

*gpu_data = NULL,

28

size_t gpu_size = 0);

29

vector<double> dcuda_host_get_timings(dcuda_host_context_handle ctx);

31

32

void dcuda_host_finish(dcuda_host_context_handle ctx);

```

**Listing 3.3:** DCuda Host API

#### 3.3.2 Device API

The device API can only be used within dCUDA kernel code. Most of the functions must be called collectively by all threads in the same rank with some exceptions. Not following the dCUDA calling conventions can lead to deadlocks or undefined behaviour.

Listing 3.4 shows the dCUDA library function to initialize the dCUDA ranks as well as some timing functions. dCUDA passes a *dcuda\_context\_handle* as an argument to the kernel it

#### 3 Programming Model

```

//Types

typedef struct dcuda_context* dcuda_context_handle;

2

struct dcuda state;

3

4

//Constants

using dcuda_comm = int;

6

#define DCUDA COMM WORLD 0

#define DCUDA_COMM_DEVICE 1

8

10

//Functions

_device__ void dcuda_gpu_init(dcuda_context_handle dcuda,

11

dcuda state& qst);

12

13

_device__ void dcuda_gpu_finish(dcuda_state& gst);

14

15

_device__ void dcuda_get_data(dcuda_state& gst,

16

void **gpu_data);

17

18

_device__ void dcuda_comm_size(dcuda_state& gst,

19

dcuda_comm comm, int *size);

20

21

_device__ void dcuda_comm_rank(dcuda_state& gst,

22

dcuda_comm comm, int *rank);

23

24

25

_device__ void dcuda_start_cpu_timer(dcuda_state& qst);

26

_device__ void dcuda_stop_cpu_timer(dcuda_state& gst);

27

```

Listing 3.4: dCUDA device API, initialisation and timing

launches. The dCUDA context stores all necessary information to initialise the individual ranks on the device. The struct *dcuda\_state* stores the state of the individual ranks and has to be stored in rank local CUDA shared memory. All dCUDA device functions require a *dcuda\_state* as a library handle. The constants *DCUDA\_COMM\_WORLD* and *DCUDA\_COMM\_DEVICE* define the two exclusive dCUDA communicators.

**dcuda\_gpu\_init** must be called before any other call to the dCUDA device library. It initialises the rank local *dcuda\_state*, which must be stored in CUDA shared memory. The initialisation requires the *dcuda\_context\_handle* that is passed to the kernel as the only argument. This function has to be called by all dCUDA ranks and all threads within a rank. It synchronises all dCUDA ranks in the system with a global barrier.

**dcuda\_gpu\_finish** frees all dCUDA resources on the device. After calling *dcuda\_gpu\_finish* no library functions can be called. This function has to be called by all ranks in the system. It performs a global barrier.

**dcuda\_get\_data** returns a pointer to the user data in the second parameter. It holds custom data passed to dCUDA with the call to the host function *dcuda\_host\_run*. After the execution

of the kernel, dCUDA copies the user data back to the host, making all the changes made to the user data visible on the host.

**dcuda\_comm\_size** takes a communicator in the second parameter and returns the size of the communicator in the last parameter. Calling this function and passing the communicator *DCUDA\_COMM\_DEVICE* will return the number of thread blocks on this device, while it will return the total number of ranks in the system if the world communicator is passed. This function can be called by individual threads without synchronisation.

**dcuda\_comm\_rank** returns the rank index at the given communicator. A rank in the device communicator returns the block index (blockIdx.x), while a rank in the world communicator returns rank\_start + blockIdx.x. This function can be called by individual threads without synchronisation.

```

_device__ void dcuda_comm_barrier(dcuda_state& gst,

2

dcuda comm comm);

3

_device__ void dcuda_win_create(dcuda_state& gst,

4

dcuda_comm comm, void *winbase,

5

6

int size, dcuda_win *win);

7

_device__ void dcuda_win_free(dcuda_state& gst,

8

9

dcuda_win win);

10

_device__ void dcuda_notify(dcuda_state& gst,

11

int rank, dcuda_comm comm,

12

13

int tag);

14

_device__ void dcuda_put(dcuda_state& gst,

15

dcuda_win win, int rank,

16

int offset, int size,

17

void *buffer);

18

19

_device__ void dcuda_put_notify(dcuda_state& gst,

20

dcuda win win, int rank,

21

int offset, int size,

22

void *buffer, int tag);

23

24

_device__ void dcuda_win_flush(dcuda_state& gst,

25

dcuda_win win);

26

27

_device__ int dcuda_test_notifications(dcuda_state& gst,

28

int tag, int count);

29

30

_device__ void dcuda_wait_notifications(dcuda_state& gst,

31

int tag, int count);

```

Listing 3.5: dCUDA Device API: Notified RMA

**dcuda\_start\_cpu\_timer**, **dcuda\_stop\_cpu\_timer** starts, respectively stops a timer. The actual measurements are done by the CPU, making it independent from GPU clock rate changes.

#### 3 Programming Model

Both functions send a message to the host causing it to take the current CPU time. Whenever the function  $dcuda\_stop\_cpu\_timer$  is called, the host stores the difference in time since the last call to  $dcuda\_start\_cpu\_timer$ . The host function  $dcuda\_host\_get\_timings$  returns all timing results. Both functions need to be called collectively by all ranks of the device.

Listing 3.5 shows relevant functions for communication and notified remote access. Before ranks can send data to each other, they have to create a memory window in a communicator, exposing memory to remote access. The window object can then be used to put data to remote memory regions.

**dcuda\_comm\_barrier** synchronises all ranks of that communicator. The function has to be called by all ranks in the communicator. Otherwise, some ranks might deadlock and never return from the function. The function guarantees that no thread will leave the barrier before all threads in the communicator have entered the corresponding barrier call.

**dcuda\_win\_create** creates a memory window for RMA in a communicator and returns a *dcuda\_win* object as the last parameter. The function has to be called by all ranks in the communicator that is given to the function and synchronises them. Each window is associated with a communicator and can only be used for communication within this communicator. The *winbase* points to the start of the memory region in GPU global memory that a rank wants to expose to remote accesses and *size* is the number of bytes of that memory region. Windows of ranks on the same device may or may not overlap. If memory windows do overlap and a remote rank writes to that region, only the target rank is notified. If window creation fails, this function returns DCUDA\_WIN\_NONE. Note that windows are only used for memory accesses but not by the notification system. Notifications are not associated with a window but rather with a tag value.

**dcuda\_win\_free** destroys the window object created earlier. It has to be called by all ranks in the communicator associated with this window object. It synchronises all the calling ranks.

**dcuda\_notify** is called by a single rank and sends a notification to some other rank with a tag. The tag has to have a value between 0 and 255. The parameter *rank* defines the target rank index of the notification in the communicator specified with the parameter *comm*. Note that ranks have different rank indices in different communicators.

**dcuda\_put** accesses and writes memory to the memory window of another rank. The parameter *win* takes a window object created earlier with *dcuda\_win\_create* and the parameter *rank* takes the rank index of the target rank in the communicator associated with the window object. The memory will be written to the memory starting at winbase + offset, whereas winbase corresponds to the memory location that was given at window creation by the target rank. The parameter *size* says how many bytes will be copied and *buffer* points to the send buffer of the calling rank. Note that the target rank will not be notified by any memory accesses

by calling this function. The target rank has to be notified eventually with a call to *dcuda\_notify* or *dcuda\_put\_notify*.

**dcuda\_put\_notify** combines the functions *dcuda\_put* and *dcuda\_notify* in a single message. It includes the parameters of both functions and the target rank will be notified as soon as the data is ready to use.

**dcuda\_win\_flush** blocks the calling rank until all previous outgoing messages associated with a window object are completed. The *dcuda\_put* functions return immediately after issuing a send request. Modifying the send buffer after a put is unsafe and can alter the data that is sent to the target. Therefore, a rank can call *dcuda\_win\_flush* before modifying the send buffers, which guarantees that all put request are completed. The function *dcuda\_notify* does not affect this function as no send buffers are involved.

**dcuda\_test\_notifications** verifies if one or more notifications with a specific tag have been received. The function tries to find *count* many notifications with the tag *tag*. The function consumes the notification and returns the value 1 if there are enough notifications ready with the right tag. If there are not enough notifications, it returns with the value 0 without consuming any notifications. Note that we cannot test for notifications from a specific source rank. The programmer can encode the source information into the tag if needed.

**dcuda\_wait\_notifications** is a blocking variant of the function *dcuda\_test\_notifications*. If the rank does not have enough notifications with the right tag, it blocks until at least *count* notifications with the right tag are ready for consumption. This function has the same behaviour as a call to *dcuda\_test\_notificcations* that returns 1.

## 3.3.3 Interface Changes

The interface of dCUDA as described here in the thesis went through several changes in respect to the initial interface [8]. We extended the interface to have a broader range of functions. This allows the user to create programs with more fain grained and tuned communication patterns. On the other hand, some functions were simplified to improve the performance of dCUDA by reducing library overhead and reducing the communication latency.

### **CPU timing**

Support for CPU timing was introduced in this thesis with the functions *dcuda\_start\_cpu\_timing* and *dcuda\_stop\_cpu\_timing*. The functions use the infrastructure provided by dCUDA to send a message to the CPU, starting or stopping a timer on the CPU.

A programmer who wants to measure the runtime of his applications can either use the CUDA functions *clock* and *clock64* to get the current 32 bit or 64 bit clock counter respectively, or he

#### 3 Programming Model

can use the dCUDA CPU timer functions. The result of the CUDA clock functions depend on the clock rate of the GPU shader clock, which may change during execution due to the Nvidia GPU boost technology. Furthermore, the programmer has to handle counter overflows to get an accurate timing result and measurements over a long period of time are difficult due to the counter overflows. The dCUDA CPU timing functions provide an alternative way to measure time periods, which is easy to use. To start and stop the timers, a message to the CPU is required, which needs around  $2\mu s$ . Therefore, we state that the precision of the function is in the range of less than  $5\mu s$ .

### **Put and Notify**

The functions *dcuda\_put* and *dcuda\_notify* are new in the interface of dCUDA. Previously, the only way to communicate with other ranks were the *dcuda\_put\_notify* and *dcuda\_get\_notify* functions, which access remote memory and notify the target rank. The new functions allow to access memory and notify a target rank individually, giving the programmer more freedom on how to design his applications. The notify function allows for fine-grained synchronisations of communication ranks without sending actual data and therefore causing less overhead. Additionally, a rank can notify other ranks without first creating a dCUDA window.

The put function does not notify the target rank. It is useful in case one wants to send multiple non-contiguous memory blocks. The sender might want to notify the target only when all the memory blocks have been transferred. By using the put function and only at the end calling put\_notify, the overhead of delivering a notification is reduced to a minimum. Note that a put\_notify is conceptually the same as a put followed by a notify to the same rank, but put\_notify yields less overhead as only one message is sent instead of two. All put and notify messages to the same remote rank are guaranteed to be received in the same order they were sent.

#### Get