Dynamic random-access memory

Dynamic Random-Access Memory kortweg DRAM (in het Nederlands - dynamisch geheugen met willekeurige toegang) is een type RAM waarbij iedere informatiebit als een elektrische lading in een kleine condensator van een adresseerbare geheugencel wordt opgeslagen. De kleine opgeslagen lading lekt echter weg en moet daarom periodiek worden uitgelezen en teruggeschreven om de lading op peil te houden. Vanwege dit verversen wordt het dynamische RAM genoemd, in tegenstelling tot statische RAM SRAM waarvan de geheugencel uit een flipflop met zes transistors bestaat.

Een hoge dichtheid van dynamische geheugencellen kon maar worden bereikt door hun integratie op een halfgeleiderschijf met behulp van lithografische technieken. Een groot aantal geheugencellen worden daarbij in een matrix van rijen en kolommen geplaatst waarin ieder cel afzonderlijk adresseerbaar is. De volledige geheugenmatrix moet met de regelmaat van de klok ververst worden, dus met een leesversterker gelezen en weer teruggeschreven worden. Dit wordt door de hardware in de geheugenchip zelf gedaan. De hardware in de geheugenchip maakt het mogelijk om een hele rij van de matrix ineens efficiënt te verversen, waarbij de gegevens niet buiten de chip hoeven te komen.

DRAM's en SRAM's verliezen de gegevens als de voedingsspanning wegvalt en worden daarom ook vluchtige geheugens genoemd.

Constructie en integratie van de dynamische geheugencel

[bewerken | brontekst bewerken]Het spreekt voor zich dat hoge dichtheden van enkele honderdduizenden tot miljoenen geheugencellen maar kunnen gerealiseerd worden door hun integratie op een halfgeleiderschijf [1]. Voor 1968 bestonden de dynamische geheugencellen uitsluitend uit een combinatie van drie tot vier MOS-transistoren met een ladingsopslag in parasitaire capaciteiten (3T-1C-cellen). Ze werden onder andere toegepast in de I1103 chip van Intel, de eerste commerciële DRAM met een capaciteit van 1 kbit die in 1970 op de markt verscheen. Deze DRAM bestond uit P-kanaal-MOS-transistoren en had als bijzonderheid het gebruik van poortelektroden bestaande uit een P+ zwaar gedoteerd polykristallijne siliciumlaag in plaats van een gebruikelijke metaallaag. Zodoende werd de drempelspanning van de MOSFET's verlaagd tot 1,6 V in plaats van de 2,7 V voor aluminium. De oppervlakte nodig voor het plaatsen van deze cellen was echter groot wat hun aantal per vierkante millimeter tot enkele duizenden beperkte.

In 1968 kwam daar verandering in toen Robert H. Dennard van IBM een geheugencel uitvond die slechts uit twee componenten bestaat namelijk een MOSFET en een MOS condensator waarin een lading kon worden opgeslagen. De MOS-transistor doet dienst als schakelaar om de ladingstoestand van de condensator te veranderen of deze te ondervragen. Er zijn slechts twee actieve geleiderbanen nodig om deze operaties uit te voeren, de zogenaamde woordlijn en bitlijn. De geheugencel wordt bij de kruising van deze leidingen aangebracht. Met een geheugencel die slechts uit twee componenten bestaat kunnen nu zeer grote integratiedichtheden worden bekomen waarbij een groot aantal cellen in een matrix worden geplaatst. Elke cel van de matrix kan afzonderlijk worden geadresseerd. Aangezien de lading opgeslagen in de condensator na verloop van tijd wegebt is het nodig om zijn ladingstoestand regelmatig te verversen. Dit proces wordt regeneratie genoemd. Alle schakelingen nodig om het geheugen te besturen namelijk de adressering, het schrijven, het lezen en het regenereren worden met behulp van de MOS-technologie op dezelfde schijf aangebracht zodat het aantal aansluitingen buiten de chip beperkt blijft.

De eerste 1T-1C-DRAM-geheugens die op de markt verschenen werden gefabriceerd met behulp van de bestaande planaire NMOS-technologie waarbij zowel de poortelektrode als de condensatorplaat uit één enkele op het siliciumdioxide neergeslagen metaallaag bestaat. De bitlijn bestaat uit een langgerekt zwaar gedoteerd N+-gebied in een P-type silicium substraat en bevat de brongebieden van een aantal in rechte lijn staande MOSFET's. De N+-afvoergebieden van deze MOSFET's zijn verbonden met een uitgestrekt N+-gebied welke de tweede plaat van de condensator uitmaakt.

De woordlijn is een lange metalen geleider boven op het met siliciumdioxide bedekte halfgeleideroppervlak en strekt zich loodrecht uitstrekt ten opzichte van de bitlijn. Op de kruising van woord- en bitlijn bevindt zich de geheugencel. Extensies van de woordlijn vormen de poortelektroden van een rij MOSFET's. Zoals men kan zien op de afbeelding, wordt de oppervlakte ingenomen door deze metaal-metaal-cel hoofdzakelijk bepaald door de oppervlakte van de MOS-condensator. De geheugendichtheid werd daardoor beperkt tot een vierduizendtal cellen (4 kbits) per chip. Om een hogere dichtheid te bekomen moesten de dimensies van zowel de condensator als die van de MOSFET alsook hun onderlinge afstand worden verkleind. Door gebruik te maken van een enkelvoudige zwaar gedoteerde N+-polykristallijne laag waaruit zowel de poortelektroden als de condensatorplaten (1-polySi-cel) konden worden gevormd werd de dichtheid met een factor zestien (64 kbits) opgevoerd. Het gebruik van N+-polykristallijn silicium als geleiderlaag maakte nieuwe en verbeterde fabricagetechnieken noodzakelijk met onder andere de inzet van oxide- en nitridelagen (ONO) om de nodige maskeringen te kunnen uitvoeren. Het fabricageproces omvatte het gebruik vier tot vijf lithografische maskers, die zeer nauwkeurig ten opzichte van elkaar moesten worden gealigneerd. Korte tijd nadien werden er zelfs twee afzonderlijke PolySi lagen toegepast, een voor de condensatorplaat en een tweede voor de poortelektrode (double polysilicon cell). Dit leidde tot een verdere verkleining van de geheugencel. De 16.384 × 1 bit DRAM-chip MM5290 van National Semiconductor is hier een voorbeeld van.

Om de dichtheid nog verder te verhogen moesten de dimensies van alle componenten op de chip worden verkleind, dus ook die van de perifere logische schakelingen. Hiervoor werd het concept van schaling toegepast waarbij niet alleen de geometrische dimensies maar ook de voedingsspanning en de dopingconcentraties op gecoördineerde wijze werden aangepast. Wil men een DRAM-versie maken met een voedingsspanning van 6 V in plaats van 12 V dan moet men een schaalfactor K toepassen van 6/12 = 0,5. De laterale en verticale dimensies worden met de helft gereduceerd terwijl de dopingconcentraties moeten verdubbeld worden. De geheugendichtheid neemt toe met een factor 1/K² (256 kbits) en het gedissipeerde vermogen per cel neemt af met een factor K² = 0,25 zodat het vermogen per oppervlakte-eenheid gelijk blijft (= 1). Een typische geschaalde geheugencel heeft de volgende karakteristieken: poortlengte MOSFET = 2 µm, dikte poortoxide = 250 ångström, diepte N+P-overgang 0,3 µm, oppervlakte per bit = 40 µm². Om de weerstand en de capaciteit van de bitlijn te verlagen gebruikt men dikwijls een aluminium geleider die op regelmatige plaatsen bitlijnsegmenten contacteert.

Het schalingsconcept kent natuurlijk zijn grenzen omdat op een gegeven moment de oppervlakte beschikbaar voor de condensator te klein wordt en dus ook de lading die kan worden opgeslagen. Deze lading is immers proportioneel met de oppervlakte. Als de leesversterkers niet meer in staat zijn om bij het lezen het onderscheid te maken tussen de aanwezige elektrische ruis en de ladingstoestand van de geadresseerde cel dan is de limiet bereikt.

Een verdere verhoging van de dichtheid kon slechts worden bekomen door de structuur en opbouw van de condensator te verbeteren zodat een grotere lading kan worden opgeslagen. In DRAM's met een capaciteit groter dan 256 kbits worden twee structuren met succes toegepast. De eerste gebruikt een gestapelde condensator die aangebracht is boven op het oppervlak van de geheugencel en nagenoeg het ganse oppervlak daarvan bedekt. In deze STC-cel (stacked capacitor cell) kan voor het dunne condensator diëlektricum (isolatielaag) een materiaal met een hoge permittiviteit zoals Si3N4 of Ta2O5 worden gebruikt. De tweede structuur vergroot het oppervlak van de condensator door gebruik te maken van de derde dimensie en de condensator aan te brengen in een groef of put die vooraf in het halfgeleideroppervlak werd weggeëtst (Trench Capacitor 3D-cell). De groef of put wordt voorzien van een oxide-nitride-oxide (ONO) isolatie laag en wordt dan met een laag zwaar gedoteerd polykristallijn silicium opgevuld die als condensatorplaat zal fungeren.

De geheugenmatrix

[bewerken | brontekst bewerken]

In de meeste gevallen wordt de geheugenmatrix opgesplitst in blokken of submatrices. De voornaamste reden hiervoor heeft te maken met de plaatsing van de leesversterkers en buffers waarvan de breedte groter is dan die van in één kolom geplaatste geheugencellen. Plaatst men ze aan de rand van één enkele matrix dan worden de bitlijnen nodeloos lang zodat hun capaciteit en hun weerstand toenemen. Het gevolg van het eerste is een afname van het nuttige signaal bij het lezen van de condensatorinhoud en van het tweede een verlaging van de snelheid waarmede de bitlijn geladen wordt. Tevens moet de afstand tussen de bitlijnen voldoende groot worden genomen wat de geheugendichtheid nadelig beïnvloed. Plaatst men de leesversterkers tussen twee blokken (open bitlijn-architectuur - OBLA) dan wordt de lengte van de bitlijn gehalveerd en dus ook haar capaciteit en weerstand. Om meer ruimte tussen de bitlijnen te creëren en de elektrische interferentie tussen de woordlijnen en de bitlijnen te verkleinen werden later de halve bitlijnen teruggevouwen zodat ze naast elkaar kwamen te liggen (folded bitline architecture - FBLA) . Op de kruising tussen de woordlijn en de bitlijn is er nu alternerend een geheugencel aanwezig. De leesversterker is aangesloten op twee naast elkaar gelegen actieve bitlijnen waarvan de karakteristieken nu nagenoeg identiek zijn, zodat er geen onbalans meer is tussen beiden. Stoorsignalen aanwezig op beide bitlijnen worden door de leesversterkers die werken als verschilversterkers automatisch weggewerkt. De leesversterkers bevinden zich nu aan de ene kant van de matrix en de kolomdecoders aan de andere kant.

Als voorbeeld van een onderverdeling in blokken nemen we een dynamisch geheugen van 1024 bits met 1024 woorden van 1 bit (1 kbit). Om 1024 cellen te adresseren heeft men log2 1024 =10 adreslijnen nodig. Een mogelijke organisatie in een enkele matrix kan verkregen worden met behulp van 64 woordlijnen en 16 bitlijnen. Een opsplitsing in twee submatrices geeft 32 woorlijnen met 16 bitlijnen voor elke matrix. Voor het adresseren van één enkele woordlijn heeft men nu log2 64 =6 adreslijnen nodig en voor het adresseren van één enkele bitlijn slechts log2 16 =4, samen 10 adreslijnen.

Werking

[bewerken | brontekst bewerken]

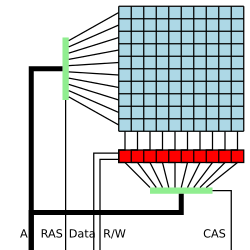

Een chip met dynamische RAM heeft de adreslijnen gemultiplext. Dat wil zeggen dat er slechts de helft van het benodigde adreslijnen is en dat het adres in twee stappen wordt overgedragen, namelijk de rij en de kolom.

Om een bit te lezen of te schrijven, gaat men als volgt te werk.

De helft van het adres (meestal de laagste bits) wordt op de adresingangen (A) gezet. De lijn RAS (row address strobe) wordt geactiveerd.

De rijadresdecoder (groen) decodeert het adres en selecteert een rij uit de matrix (blauw, zie afbeelding rechts) van geheugenelementen. De hele rij wordt naar de buffer (rood) gekopieerd.

Nu wordt de lijn R/W (read/write) op het juiste niveau gezet en wordt (als er geschreven wordt) het databit op de lijn data gezet.

Daarna wordt de andere helft van het adres op de adresingangen gezet en de lijn CAS (column address strobe) geactiveerd. De kolomadresdecoder (groen) decodeert het adres en het databit wordt in de buffer opgeslagen, of een bit wordt uit de buffer op de datalijn gezet.

Ten slotte worden CAS en RAS weer inactief gemaakt. Op het moment dat RAS inactief wordt, wordt de buffer terug gekopieerd naar de juiste rij van de matrix (blauw) en toont de datalijn het door CAS geselecteerde bit.

Er is dus voor elk bit een blauwe matrix nodig. De getoonde schakeling correspondeert veelal met een chip, zodat 8-bits geheugen dan 8 chips parallel nodig heeft.

Fast page mode DRAM (FPM DRAM)

[bewerken | brontekst bewerken]Met fast page mode DRAM (FPM DRAM) is het mogelijk achter elkaar meerdere bits van dezelfde rij direct uit de buffer te lezen. Eerst wordt RAS geactiveerd. Daarna kan de processor met CAS de bits in de buffer adresseren. Ten slotte wordt RAS weer gedeactiveerd.

Refresh

[bewerken | brontekst bewerken]Uit het bovenstaande blijkt dat een hele rij uit de matrix ververst wordt door de rij te lezen. Het gebruik van CAS is daarbij niet nodig.

Aparte datalijnen

[bewerken | brontekst bewerken]Sommige DRAM-chips hebben een aparte in- en uitgang voor data. De uitgang is echter tri-state en niet zelden worden in- en uitgang op de printplaat direct met elkaar verbonden.

- ↑ Dynamic Semiconductor RAM Structures, Pergamon Press Ltd., april 1984, EPO Applied Technology Series, A patent-oriented survey, vol. 1, A. Cardon & L.J.L. Fransen, ISBN 0-08-030578-4